## menta

#### eFPGA - Key solution for Automotive SoCs

Grenoble, France December 6<sup>th</sup> 2017

## mente

#### eFPGA - Key solution for Automotive SoCs

Imen BAILI Sales Application Engineer

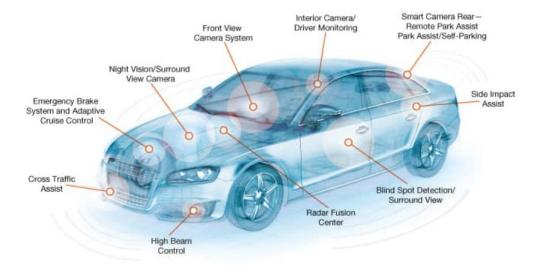

## Classical Automous ADAS Distributed Systems

**Distributed architecture and thus**

**Distributed Intelligence !**

Current - latest ADAS features are software driven and use data from many sources

- ✓ Systems must work & communicate together

- ✓ Data must be shared

## Classical Autonomous driving solutions

#### Full Distributed Approach issues & Level 5 autonomy ?

- ✓ Unacceptable System Latency in the transfer of safety critical information

- ✓ Loss of potentially useful data at the edge nodes

- Rapid increase in Cost and Power consumption as driver assist systems become more complicated (SW & HW)

How to scale up from this architecture to reach Level 5 autonomy ?

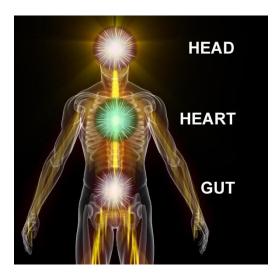

### **ADAS Systems Requirements** using eFPGA

- **Real time processing**

- Deterministic Situation Awarness & Decision-making

- Long period of life in the field and need to evolve overtime because of evolving standards and/or algorithms

- **Reconfigurability**

- Large BW & Very Low Latency

- Sensors Fusion, Anticipation & Prediction for avoiding upcoming accidents Artificial Intelligence algorithms

- Data parallel processing

- Hardware & Software integration Satisfying Embedded contraints Small PCB

- Low system size as possible

- Low cost

- Low power

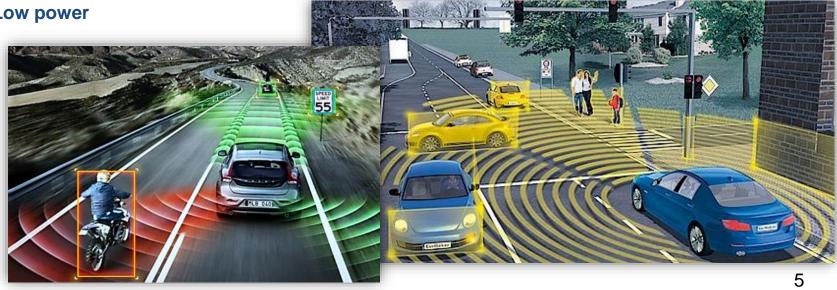

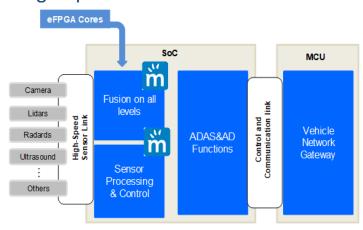

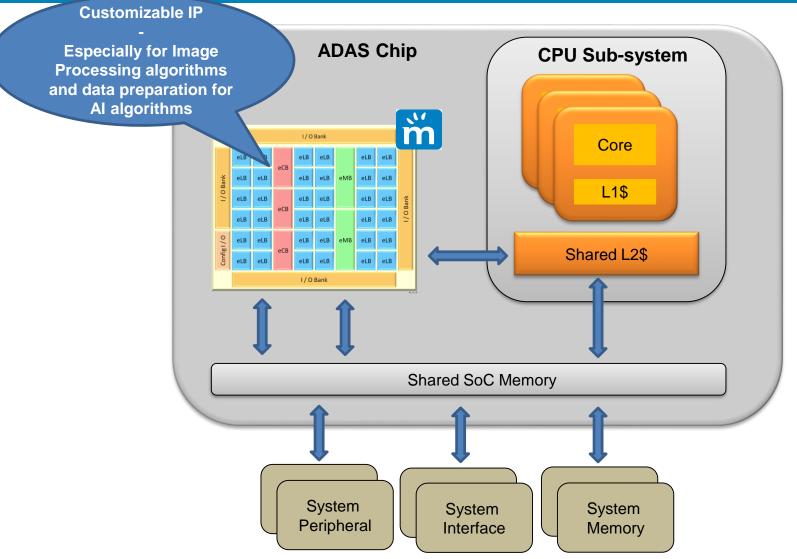

## ADAS Centralized Processing Approach

Think Centralized Processing approach to face Level 5 Autonomy Challenges !

Use eFPGA for performing Raw Sensor Data fusion inside a central ADAS processing unit:

- Raw Data Fusion Centralization

- Expand ADAS processor role to include fusion of raw data

- Avoid executing Image-processing separately from the CPU

- Remove as maximum as we can Chip-to-Chip useless high speed bus interfaces adding penalty latency

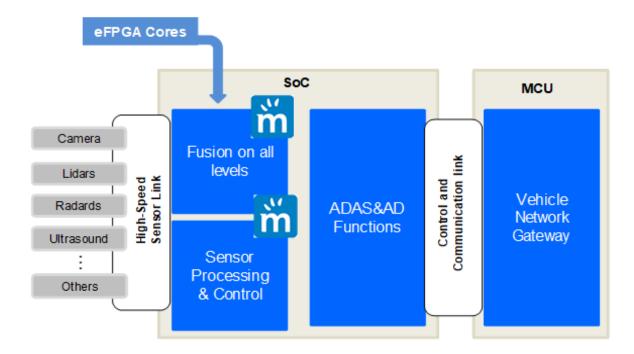

#### **Architecture Solution ?**

eFPGA IP combination with CPU in a unified ADAS architecture

## ADAS Centralized Processing Approach

In fact, in addition of the traditional sensor fusion, the raw data allow cars to view the external environment more clearly and to get "<u>redundancy</u>" checking!

Menta is the only eFPGA vendor offering a standard scan chain interface with a TC in excess of 99.8%

## ADAS Centralized Processing Approach

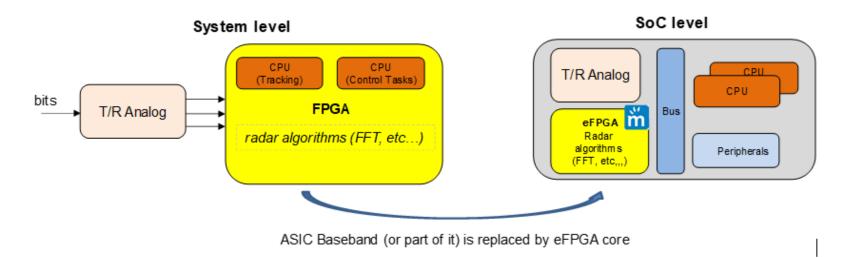

## **LIDAR Systems**

#### eFPGA in LIDAR Systems:

It improves also performance in term of Image Processing thanks to eFPGA dedicated blocks like complex DSP for FFT computing, complex multipliers and FIR Filters.

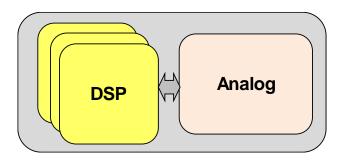

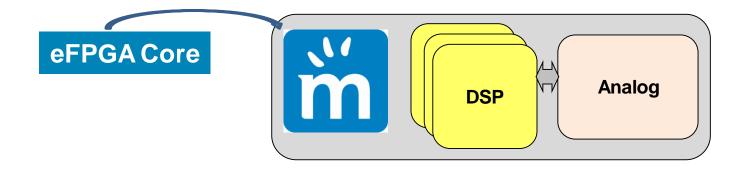

## **Battery Monitoring Systems**

Battery Monitoring Systems - Legacy Hardware Architecture:

Battery Monitoring Systems - Proposal Hardware Architecture using Menta eFPGA:

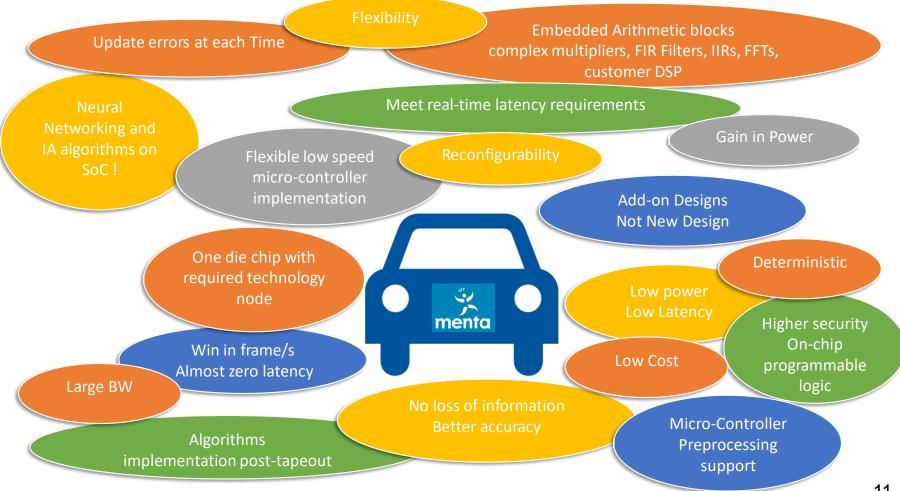

## Menta eFPGA advantages in Automotive Systems

### Menta eFPGA benefits

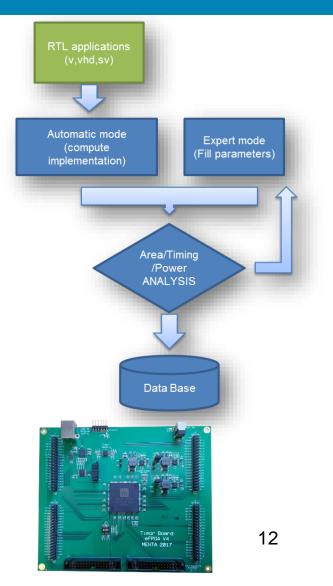

- All parameters can be defined based on customers need. Custom performances, power and area trade-off. Unique specification software

- Easy integration. Fully verifiable within customer flow and up to post place & route gate level simulation

- Catalogue of arithmetic blocks available from simple MAC to complex programmable DSPs for FIR filters, FFT, complex multipliers, etc.

- Multiple tapeouts in various technology nodes: STM 130, STM 65, TSMC 28HPC+, GLOBALFOUNDRIES 14LPP

- Including MRAM based eFPGA

- TSMC OIP Symposium

- At GLOBALFOUNDRIES 32SOI & 14LPP catalogue

- Member of 22FDX Ecosystem

# en baili@menta-efpga.co

imen.baili@menta-efpga.com www.menta-efpga.com

Thank You