|

|

|

www.design-reuse-embedded.com

www.design-reuse-embedded.com |

|

DCAN FD, A Configurable CAN Bus Controller with Flexible Data-Rate Targets Autonomous Cars & ADAS Systems

Poland, Bytom , Sept. 26, 2016 – Digital Core Design, an IP Core provider and a System-on-Chip design house from Poland, has introduced the newest IP Core. The DCAN FD IP Core is a configurable CAN Bus controller with Flexible Data-Rate. It conforms to Bosch CAN 2.0B specification (2.0B Active) and CAN FD (flexible data-rate) in accordance to ISO 11898-1:2015. The improved protocol overcomes standard CAN limits: data can be transmitted faster than with 1 Mbps (even up to 8Mbps) and the payload (data field) is up to 64 byte long. When only one node is transmitting, the bit-rate can be increased, because no nodes need to be synchronized.

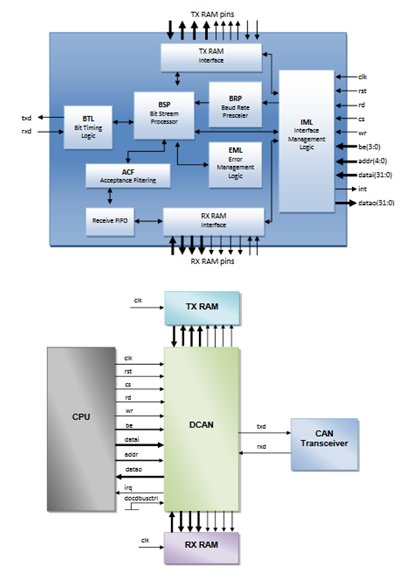

The DCAN FD is a standalone controller for the Controller Area Network (CAN), widely used in automotive and industrial applications. It conforms to Bosch CAN 2.0B specification (2.0B Active) and CAN FD (flexible data-rate) - in accordance to ISO 11898-1:2015.

Standard CAN requirements become insufficient in modern automotive. The carmakers demand more bandwidth and more throughputs for most CAN-based in-vehicle networks. The DCAN FD IP Core is also a good alternative for non-automotive projects where not the increasing speed is the target. The longer payload (more than 8 byte) becomes crucial then.

The improved protocol overcomes standard CAN limits: data can be transmitted faster than with 1 Mbps (even up to 8 Mbps) and the payload (data field) is up to 64 byte long. When only one node is transmitting, the bit-rate can be increased, because no nodes need to be synchronized. Of course, before the transmission of the ACK slot bit, the nodes need to be re-synchronized.

- The core has a simple CPU interface (8/16/32 bit configurable data width), with small or big endian addressing scheme ? explains Tomasz Krzyzak, VCEO in Digital Core Design. Hardware message filtering and 128 byte receive FIFO enable back-to-back message reception, with minimum CPU load. The DCAN FD is described at RTL level, allowing target use in FPGA or ASIC technologies.

More information: http://dcd.pl/ipcore/131/dcan-fd/

Key features:

- Designed in accordance to ISO 11898-1:2015

- Supports CAN 2.0B and CAN FD frames

- Support up to 64 bytes data frames

- Flexible data-rates supported

- 8/16/32-bit CPU slave interface with small or big endianness

- Simple interface allows easy connection to CPU

- Supports both standard (11-bit identifier) and extended (29 bit identifier) frames

- Data rate up to 8 Mbps

- Hardware message filtering (dual/single filter)

- 128 byte receive FIFO and transmit buffer

- Overload frame is generated on FIFO overflow

- Normal & Listen Only Mode

- Transceiver Delay Compensation up to three data bit long

- Single Shot transmission

- Ability to abort transmission

- Readable error counters

- Last Error Code

- Fully synthesizable

- Static synchronous design with positive edge clocking and synchronous reset

- No internal tri-states

- Scan test ready

- Available system interface wrappers:

- AMBA - APB Bus

- Altera Avalon Bus

- Xilinx OPB Bus

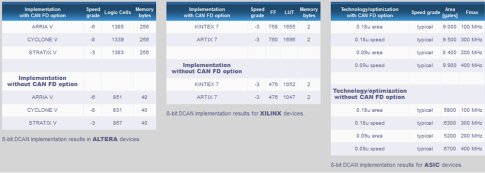

Performance:

Deliverables:

- Source code:

- VHDL Source Code or/and

- VERILOG Source Code or/and

- FPGA Netlist

- VHDL /VERILOG test bench environment

- Active-HDL automatic simulation macros

- NCSim automatic simulation macros

- ModelSim automatic simulation macros

- Tests with reference responses

- Technical documentation

- Installation notes

- HDL core specification

- Datasheet

- Synthesis scripts

- Example application

- Technical support

- IP Core implementation support

- 3 months maintenance

- Delivery of the IP Core and documentation up dates, minor and major versions changes

- Phone & email support.

Information about Digital Core Design:

The company founded in 1999, since the beginning stands in the forefront of the IP Core market. High specialization and profound customer service enabled to introduce more than 70 different architectures. Among them is the world's fastest 8051 IP Core, the DQ80251, which is more than 75 times faster than the standard solution. The same, D32PRO, which is a royalty-free and fully scalable 32-bit CPU creates new possibilities for modern projects. As an effect, over 300 hundred licensees have been sold to more than 500 companies worldwide. Among them are the biggest enterprises like e.g. Sony, Siemens, General Electric and Toyota. But a lot of DCD's customers are small businesses, R&D laboratories or front/back end offices, which require exact solution tailored to their project needs. Rough estimations say that more than 500 000 000 devices around the globe have been based on Digital Core Design's IP Cores.

Back

Back Contact Us

Contact Us