Do we still need to introduce and define RISC-V? You know, the open-source instruction set architecture (ISA) that is gaining popularity thanks to its flexibility, scalability, and modularity. Okay, we just did, just to be sure we are all on the same page. One of the key benefits and the main “raison d’être” of RISC-V is the possibility to tailor both the instruction set (ISA) and the internal design (microarchitecture) of the processor to meet specific application requirements. This customization capability extends to custom compute solutions, enabling developers to create hardware optimized for their workloads. In this blog post, let’s explore the benefits of RISC-V customization and custom compute, and industry applications.

The traditional approach to hardware design and its limits

When engineers design systems, there is always a trade-off between flexibility and performance. The most flexible approach is to choose a general-purpose core and to optimize software. You can think of it as the “Off the peg” approach to processor engineering which competitors can easily match. But this often means that algorithms are executed inefficiently and therefore run extremely slowly.

The traditional approach to overcome this problem is to create fixed-function circuits designed to perform a specific set of operations. These hardware functions can be extremely fast, but because they are hardcoded, it is difficult to modify or update them to meet, let’s say, changing application requirements.

The solution is to combine both approaches. Keep the flexibility of the software, but bring into the processor the additional logic that enables those fantastic speed-ups.

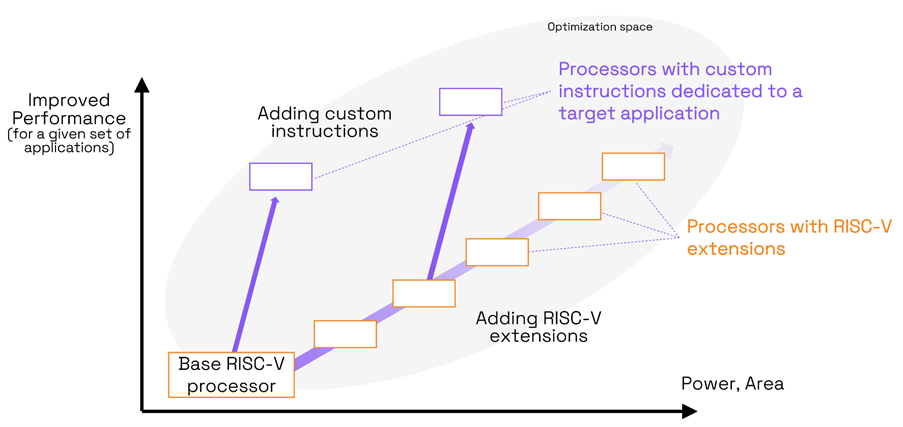

The RISC-V standard has been designed to enable this. It is modular, with many standard extensions dedicated to common use-cases, but it also allows designers to create their own additions to the ISA and modify the microarchitecture of a core to meet specific application requirements. This customization capability enables hardware optimization for a specific workload, making it possible to improve performance, power consumption, and overall efficiency.

Key benefits of RISC-V customization

Custom instructions for unique workloads

One of the key benefits of RISC-V customization is the ability to create custom instructions tailored to specific application needs. You can use custom instructions to accelerate critical operations, reduce memory access, and improve energy efficiency. For example, you could create a custom instruction to perform a specific AI algorithm, reducing the number of clock cycles required to perform the operation. We have technical papers and case studies on this, for example Embedded AI on L31 – compact neural network accelerator in CodAL. In this paper, our application engineering team looked at what could make running AI algorithms on resource-constrained embedded devices easier from a software and hardware point of view.

Hardware/software co-optimization

In order to pick custom instructions correctly and create efficient implementations, software and hardware teams need to collaborate. This is Hardware / Software co-optimization, and requires a change in methodology. It can seem uncomfortable to have to change habits, but there are significant benefits in addition to much better system efficiency. By working earlier on the processor customization, architects on both sides (hardware and software) can now collaborate from the beginning of product development. This way, the software team can start developing their critical algorithms and uncover much sooner those potential gains that could not be achieved if the hardware was already frozen.

Codasip supports this collaboration with a common language (CodAL) and tools that bring the ability to run software even before hardware designers start writing the first line of RTL!

Custom compute for optimal PPA at controlled costs

Adding custom instructions is already a very effective way to improve the efficiency of a processor. But there are many additional features that can be extremely useful. For example? You may want to increase the data throughput between the processor and interfaces or other processing elements, parallelize some operations, manage specific data types, or add application-related features. These are examples of modifications that go beyond just adding instructions, but bring benefits tailored to your application.

We call this custom compute.

Custom compute enables designers to create hardware optimized for specific types of workloads. It enables PPA gains that no process technology gain can give you, now that Moore’s law has ended.

Custom compute is particularly valuable for applications that require high performance, low latency, or high energy efficiency. But, more importantly, it enables you to get what doesn’t exist anywhere: the perfect match to your needs. This is the “Haute Couture” of processor engineering.

Improved security and reliability

The benefits of custom compute extend beyond performance and energy efficiency. Custom compute can also enable organizations to improve security by adding security features at the heart of the processor. By creating custom instructions, you can also make your software unusable for competitors while making life difficult for potential attackers, improving overall system security.

In addition, custom compute can also focus on improving reliability and reducing maintenance costs. By adding error-correcting features and special runtime hardware checks, you can reduce the risk of hardware failures and minimize downtime. Very handy in applications such as industrial IoT or automotive, for example.

Flexibility is key

In conclusion, RISC-V customization and more generally custom compute brings significant efficiency improvements. This can be achieved by a closer collaboration between hardware and software teams that needs to be supported by a strong methodology and by efficient tools. Doing all this manually would be an enormous task. This is why Codasip provides products to help you:

- RISC-V IP ready to be customized, with the ability to tailor the processor perfectly to your own application,

- And tools to help identify areas for improvement and support a hardware / software co-optimization methodology.

What if you could optimize your processor after tape-out? This is exactly what Codasip and Menta enable: extending RISC-V processors in the field with Codasip Studio and Menta eFPGA.