### Introduction to Soitec

We design and deliver innovative substrates and solutions to enable our customers' products shaping everyday life

- > **Number 1 –** Largest manufacturer of engineered substrates

- > Global presence 1,100 employees worldwide

- > Serving 4 high-volume markets Smartphones, automotive, cloud & infrastructure, IoT

- > Multi-site industrial footprint France, Singapore, China

- > Industry standard RF-SOI is in 100% of smartphones

### Choosing the right base for your product

#### Pinot Noir, Burgundy, Cabernet Sauvignon...

**End Product**

**Soil Properties**

#### **Substrate**

# Soitec's full range of engineered substrates across multiple segments and applications

## Soitec's full range of engineered substrates across multiple segments and applications

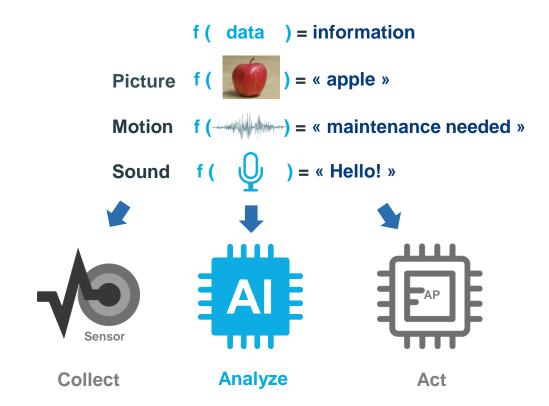

## Al is about transforming data into meaningful information

## Al is increasingly sophisticated

#### **Google Machine Learning**

Achieving Higher Word Accuracy, 2013-2017 100% Word Accuracy Rate (%) - - Threshold for Human Accuracy 70% 2013 2014 2015 2016 2017

Source: Mary Meeker's annual Internet Trends Report

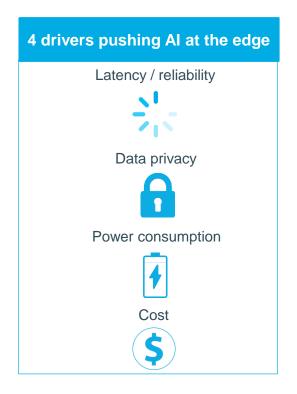

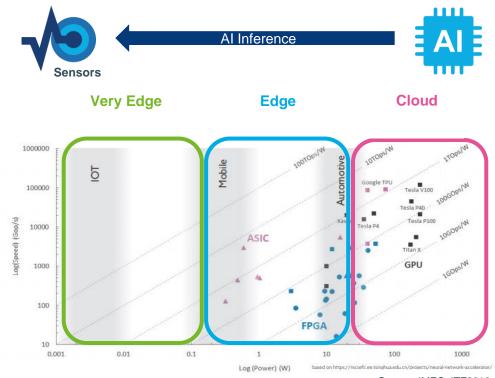

## Al inference is moving to the edge Low-power solutions are required

Source: IMEC, ITF2018

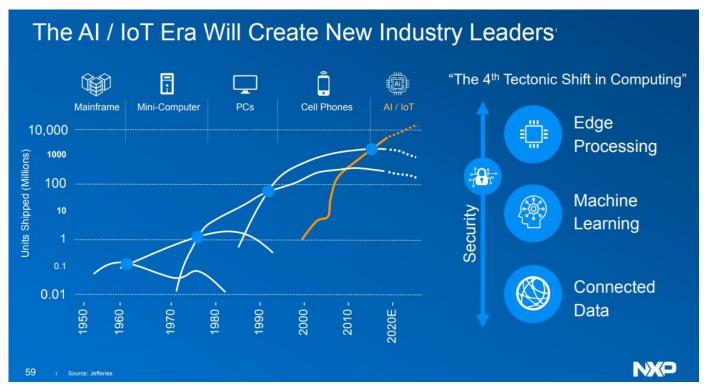

## AloT (Al + loT) sparks a new semiconductor revolution

Source: NXP Investor Day 2018

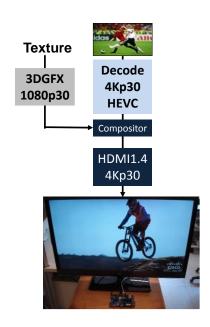

## FD-SOI – powering the AloT revolution

i.MX RT600 crossover processors unlocking the potential of machine learning and artificial intelligence at the edge, are based on FD-SOI

Powering the next generation of voice-assisted end nodes

i.MX RT600 Family of Crossover Processors

Next generation always-on FPGA low power machine learning inferencing (from 1mW to 1W)

based on FD-SOI

Designers need silicon that allows them to build compact high-performance AI devices that deliver excellent performance without violating footprint or thermal management constraints.

Cost is also a crucial factor.

Source: Lattice white paper, May 2018

Next generation Human Machine Interfaces powered by AI ambient computing based on FD-SOI

The intelligence has to move to the edge [..].Our vision requires a few things [..]. 22FDX has that mix of performance and power and the ability to aggregate functions such as RF or non-volatile memory that we are looking towards. We need also extremely low power so the ability to do active body biasing is very important to us.

Source: Synaptics CEO, GTC, September 2018

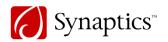

## **FD-SOI** unique features

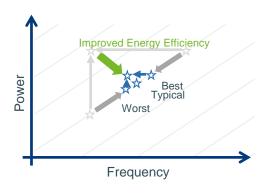

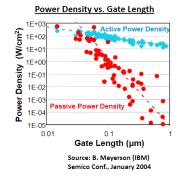

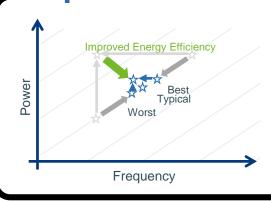

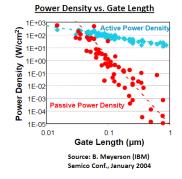

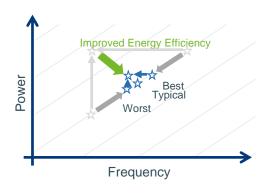

## Energy efficiency needs dynamic power/ leakage optimization techniques

Variations need to be mitigated for optimized energy efficiency

Energy efficiency needs dynamic power/ leakage

optimization techniques

Variations need to be mitigated for optimized energy efficiency

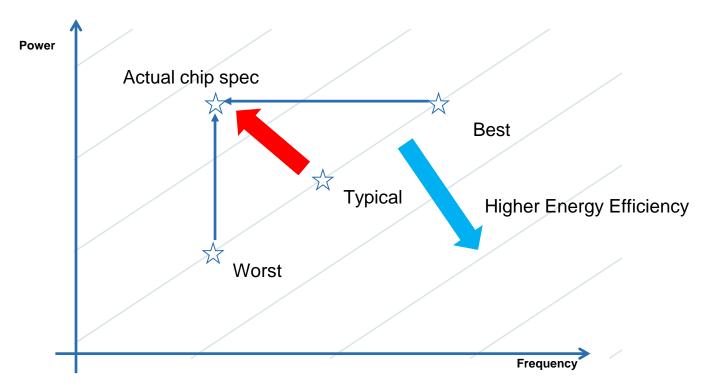

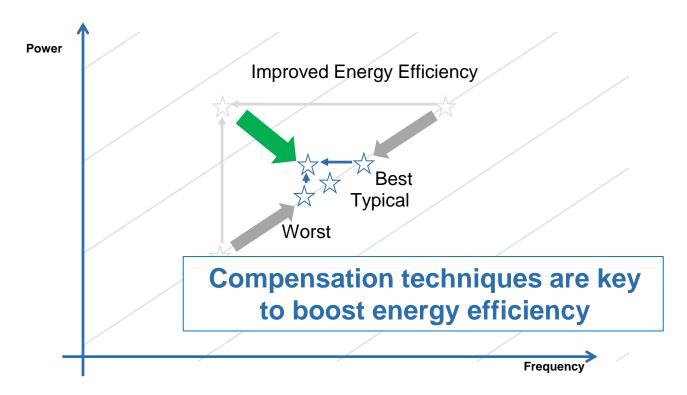

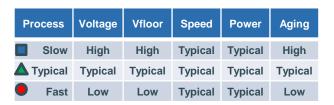

## Variations impact energy efficiency

## Variations impact energy efficiency

## Static AVS is commonly used in advanced technology nodes but faces severe drawbacks

Performance and power towards TT corner

ST, ITC 2017 - Mhira and Huard, Best Paper award

Aging is degraded

Vfloor is increased (less room for overdrive)

Temperature compensation is very difficult (too sensitive). Vdd not the right lever.

More complex voltage regulators required

# Energy efficiency needs dynamic power/ leakage optimization techniques

Variations need to be mitigated for optimized energy efficiency

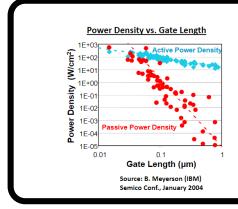

## Low Power design techniques principles

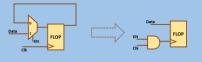

#### **Clock Gating**

- Avoid systematic toggling of Flipflops CLK pins

- ▶ Put logic in ClockTree to reduce active power

#### **Power Gating**

- Define multi-Vdd domains

- High Vdd only on-demandLow Vdd for low performance

- ) Switch off unused domains

**Dynamic Power:** ~W.V<sub>dd</sub><sup>2</sup>.F

**Leakage Power :** ~(V<sub>dd</sub>/L).e<sup>-Vth/S</sup>

**Speed**:  $\sim$ W/L ( $V_{dd}$ - $V_{th}$ )<sup>2</sup>

#### **DVFS**

- Dynamic Voltage Frequency Scaling

- ▶ Benefit from V² power savings

Landscape of low power techniques

|                  |                          | BULK (Vdd only)     |          |                      |          |

|------------------|--------------------------|---------------------|----------|----------------------|----------|

| Source           | Parameter                | Static Optimization |          | Dynamic Optimization |          |

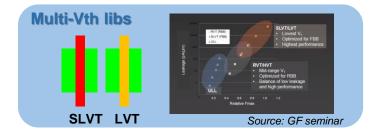

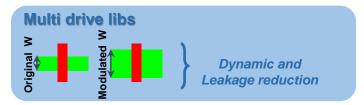

| Dynamic<br>Power | W                        | Multi-drive lib     | <b>/</b> | -                    |          |

|                  | Vdd                      | Multi-Vdd lib       | <b>✓</b> | DVS                  | <b>~</b> |

|                  | Vdd/Vth                  | Multi-Vdd/Vth lib   | <b>✓</b> | X                    | •        |

|                  | F                        | Clock Gating        | <b>\</b> | DFS                  | <b>✓</b> |

| Leakage<br>Power | L                        | Multi-L lib         | <b>✓</b> | -                    |          |

|                  | Vth                      | Multi-Vth lib       | <b>√</b> | ×                    | •        |

|                  | Switch off (Vdd)         | -                   |          | Power gating         | <b>4</b> |

| Variations       | Consumer (Vdd)           | Static AVS          | <b>\</b> | ×                    |          |

|                  | Consumer &<br>Auto (Vth) | ×                   |          | ×                    |          |

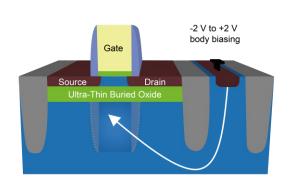

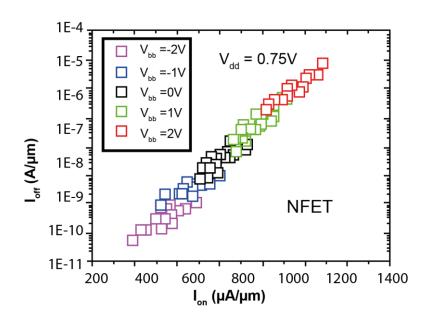

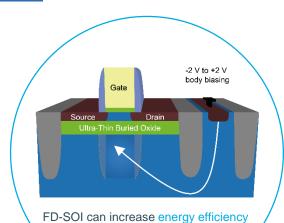

# Body-bias: a unique solution to fully control threshold voltage dynamically

Landscape of low power techniques

|                  |                          | BULK (Vdd only)     |                      | FD-SOI (Vdd + Vbb)   |                      |  |

|------------------|--------------------------|---------------------|----------------------|----------------------|----------------------|--|

| Source           | Parameter                | Static Optimization | Dynamic Optimization | Static Optimization  | Dynamic Optimization |  |

|                  | W                        | Multi-drive lib     | -                    | Multi-drive lib      | -                    |  |

| Dynamic<br>Power | Vdd                      | Multi-Vdd lib       | DVS                  | Multi-Vdd lib        | DVS 🗸                |  |

|                  | Vdd/Vth                  | Multi-Vdd/Vth lib   | ×                    | Multi-Vdd/Vth/BB lib | DV <b>B</b> S        |  |

|                  | F                        | Clock Gating        | DFS                  | Clock Cating 🗸       | DFS                  |  |

| Leakage<br>Power | L                        | Mult This is ver    | y unique!!           | Multi-L lib          | -                    |  |

|                  | Vth                      | Multi-Vth lib       | X                    | Multi-Vth/BB lib     | Dynamic ABB          |  |

|                  | Switch off (Vdd)         | -                   | Power gating         |                      | Power gating         |  |

| Variations       | Consumer (Vdd)           | Static AVS          | ×                    | Static AVS           | · .                  |  |

|                  | Consumer &<br>Auto (Vth) | ×                   | ×                    | Static ABB (P)       | Dynamic ABB (T+A)    |  |

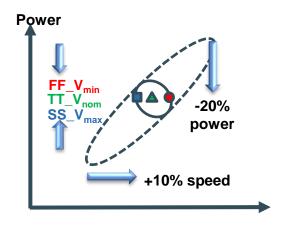

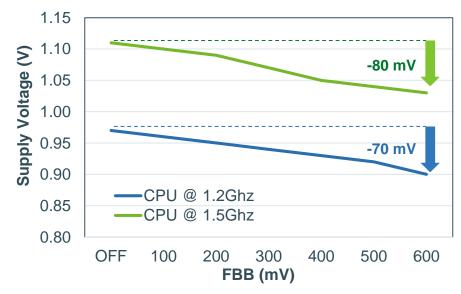

### Adaptive optimization of body-bias and Vdd

- Adaptive body-bias is demonstrated on system running real SW

- > Body-Bias enables dynamic power reduction thanks to supply voltage reduction

ST, IRPS 2018 - Huard et al., Best Paper preselected

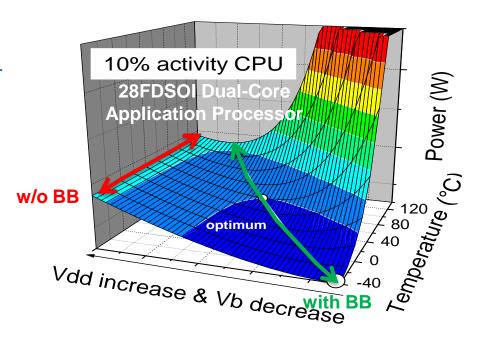

# Combining compensation and leakage optimization power mode

- An optimum body bias / Vdd exists for each temperature

- This optimum energy point cannot be accessed by bulk technologies

N.B.: Experimental results, ST IRPS 2016

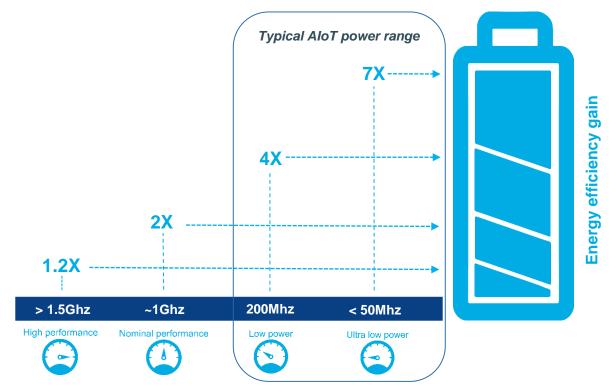

## **Body Bias**

gains by 7 by leveraging its unique body-bias capability

Body-bias impact (AVS, ABB) on energy efficiency

Source: Dolphin Integration, 2018

## **Body-bias enablement status in the industry**

| ВВ Туре                        | Market                                                |  |  |

|--------------------------------|-------------------------------------------------------|--|--|

| Static / Boost                 | Mobile, Consumer, Computing                           |  |  |

| Static / Compensation          | IoT, Automotive, Mobile, Consumer,<br>Computing, A&D  |  |  |

| Dynamic / Compensation         | IoT, Automotive, Mobile, Consumer,<br>Computing, A&D  |  |  |

| Dynamic / Boost + Compensation | IoT, Automotive, Mobile, Consumer,<br>Computing , A&D |  |  |

| Partial Not Started            |                                                       |  |  |

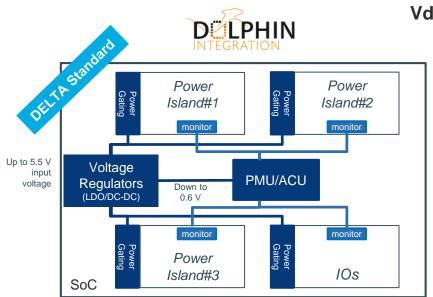

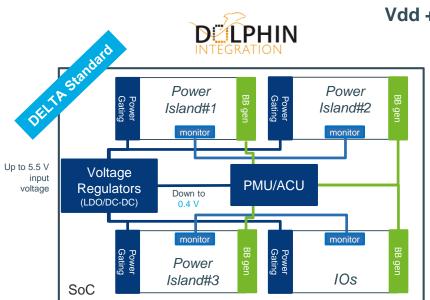

### A complete power management IP plateform...

#### **Current Dolphin Integration Solution:**

Enablement of advanced SoC power architecture to bridge the complexity gap

#### Vdd modulation

#### **Key features**

- Wide range of IP offering

- Standardized IPs for streamlined SoC integration

- Scalable according to SoC complexity

- Workable with third-party silicon IPs

- > Built-in safety features to prevent SoC failures

- > Based on silicon proven IP architectures

### ... to make body-biasing easy

#### FD-SOI project – going-on:

Enablement of Adaptive Body Biasing as turnkey solution for best Energy Efficiency without risks

#### Vdd + Vbb modulation

#### **Key evolutions**

- Enhanced Power Management IP Platform Vdd+Vbb

- Fully integrated Power Management IP platform

- Automatic reach of Optimum Energy Point

- Regulation loop for P, V, T & A compensation

- Workable with any standard-cell library & memory

- Design methodology & support

## Enabling our customers' products shaping everyday life with engineered substrates

- SOITEC is innovating through substrate technologies bringing solutions to tomorrow technology disruptions

- Al and AloT will be at the heart of the next human revolution and is moving closer to the edge

- FD-SOI offers unique power efficiency advantages though body bias technologies

- > FD-SOI adoption in AloT is ongoing and will play an increasing role in enabling this new technology disruption

## Thank you

#### Follow us on:

For more information, visit us at: