Pre-Silicon Security Evaluation

Security Verification Towards EDA

### **Pre-Silicon Security Evaluation**

#### CONTEXT

- Banking Payments

- Mobile Phone

- Smartcards

- Computers

- Laptop

- Tablet

- Aerospace & Defense

- ...

Mature Markets / Mature Security

- Automotive

- Factories

- Retail

- Health

- Machine to Machine Communication

- •

Mature Markets / Emerging Security

- Wearables

- Drones

- Smart Home

- Smart Cities

Emerging Markets / Emerging Security

### **Pre-Silicon Security Evaluation**

#### CONTEXT

### **Pre-Silicon Security Evaluation**

#### CONTEXT

#### A NEW PACEMAKER HACK PUTS MALWARE DIRECTLY ON THE DEVICE

CHOO CHIN/GETTY IMAGES

THE FIRST PACEMAKER hacks emerged about a decade ago.

But the latest variation on the terrifying theme depends not

#### A CLEVER ANDROID HACK TAKES ADVANTAGE OF SLOPPY STORAGE

ANGEL GARCIA/BLOOMBERG/GETTY IMAGES

AN ANDROID APP has two choices for where to put its data on a device: internal storage, where it's safe and snug, isolated by the operating system's sandbox, and external storage, where data can move between apps but isn't as protected. Most of the time, that setup works just fine. But when

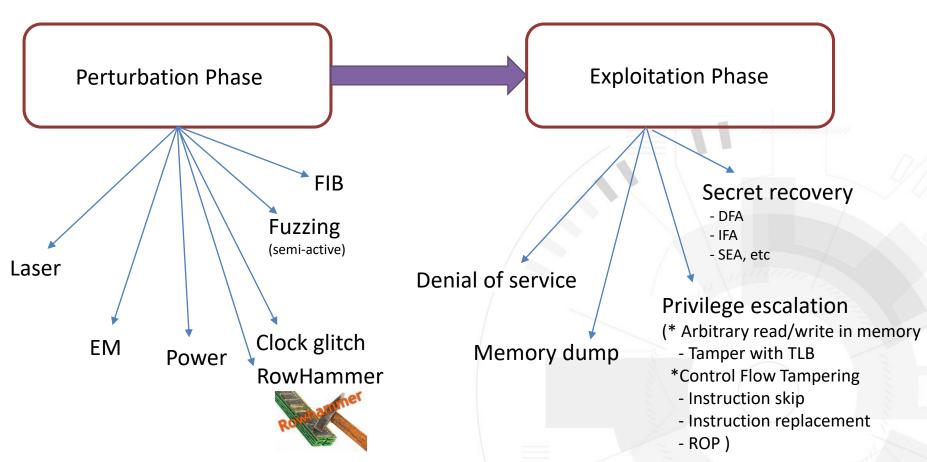

### WHAT KIND OF ATTACKS?

### **Security Evaluation**

ABOUT SECURITY THREATS

Cryptography is robust but Physical Attacks are here ...

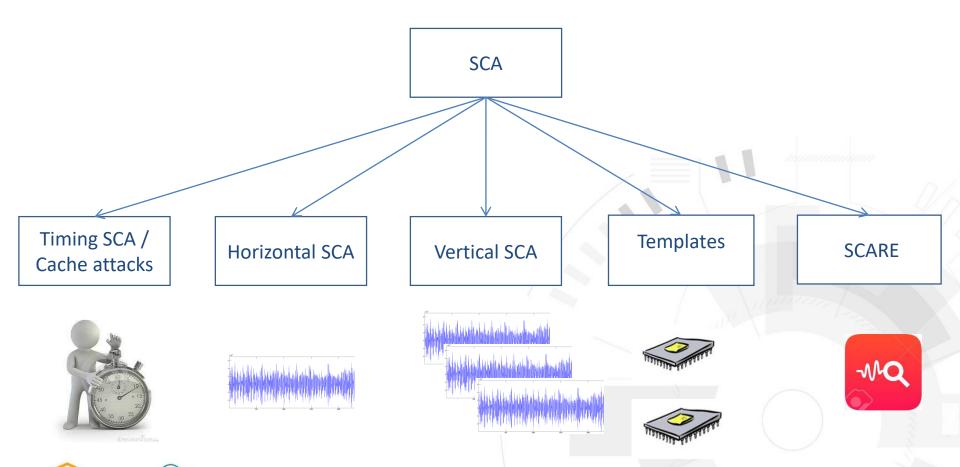

#### **Passive Analyses**

- Do not Interact directly with the target:

- → Exploit a physical property related to the activity of the sensitive data

- Common analyses: SCA (Side-Channel Analyses)

#### **Active Analyses**

- Interact directly with the target:

- → Access to the target

- → Perturbate its normal behavior

- Common analyses: FIA (Fault Injection Analyses) / Active Probing (FIB)

### **Security Evaluation**

■ ABOUT SECURITY THREATS: Active Analysis

### **Security Evaluation**

■ ABOUT SECURITY THREATS: Passive Analysis (SCA)

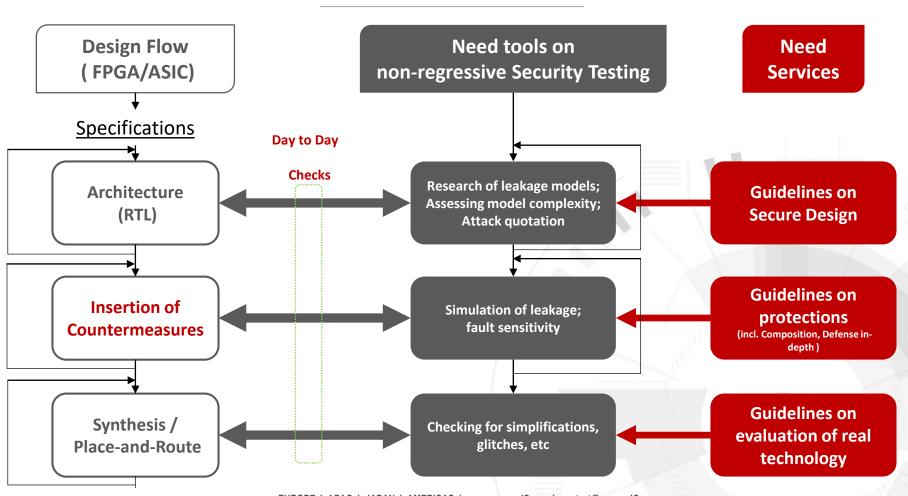

**EDA Tools for Design For Security**

### **Pre-Silicon Security Evaluation**

**■ EDA: Electronic Design Automation Axes**

#### **EDA Axes** High level Synthesis Logic Synthesis Design Schematic capture Lavout Transistor / Logic / Behavioral / HW Emulation Simulation Functional verification Formal verification Analysis & Verification Static Timing Analysis **Clock Domain Crossing Verification** Mask Data Preparation Analysis (computation failure in time rate and diagnostic) **Functional Safety** Synthesis (add reliability to structured components) Verification (run a fault campaign: error detection) RTL / PS / PR / Layout Security (SCA / FIA and more) **Security Analysis**

HW and SW Analysis

### **Pre-Silicon Security Evaluation**

Design-for-Security (DFS) approach is being universalized

### **Pre-Silicon Security Evaluation**

Design-for-Security (DFS) approach is being universalized

```

library design lib;

use design lib.aes pkg.all;

25 pentity cipher is

port(

n reset

: in std logic;

: in std logic;

: in std logic vector(127 downto 0);

key schedule

: in std logic vector(127 downto 0);

key schedule rdy

: in std logic;

round

: in std logic vector(3 downto 0);

cipher

: out std logic vector(127 downto 0));

end entity cipher;

architecture cipher arch 1 of cipher is

signal round value

: std logic vector(127 downto 0);

signal sub bytes std value : std logic vector(127 downto 0);

signal mix columns value : std logic vector(127 downto 0);

: std_logic_vector(127 downto 0);

signal shift rows value

signal add_key_output_value : std_logic_vector(127 downto 0);

signal cipher_round_value

: std_logic_vector(127 downto 0);

signal cipher s, cipher r

: std logic vector (127 downto 0);

attribute keep hierarchy : string;

attribute keep hierarchy of cipher arch 1 : architecture is "yes";

attribute equivalent register removal : string;

attribute equivalent_register_removal of cipher_r : signal is "no";

attribute equivalent register removal of cipher s : signal is "no";

attribute keep : string;

attribute keep of round value

: signal is "true";

```

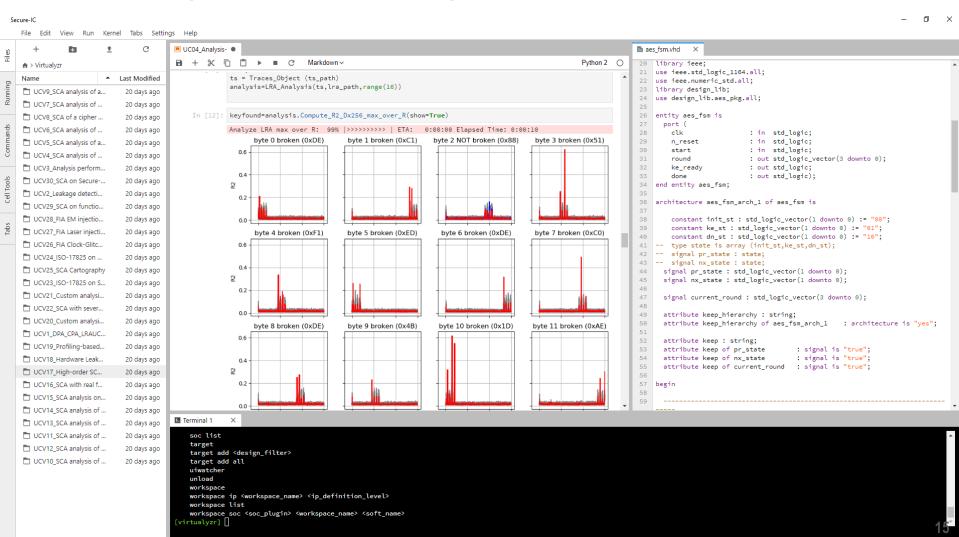

Security leaking signal detection by the VIRTUALYZR

```

22 library design lib;

use design lib.aes pkg.all;

25 mentity cipker is

port(

n reset

: in std logic;

clk

: in std logic;

: in std logic vector(127 downto 0);

: in std logic vector(127 downto 0);

key schedule

schedule rdy

: in std logic;

: in std_logic_vector(3 downto 0);

: out std logic vector (127 downto 0));

chpher

end entity cipher;

Farchitecture cipher arch 1 of cipher is

signal round_value

: std_logic_vector(127 downto 0);

signal sub bytes std value

: std logic vector(127 downto 0);

signal mix columns value

: std logic vector(127 downto 0);

signal shift rows value

: std logic vector (127 downto 0);

signal add key output value

: std logic vector(127 downto 0);

signal cipher round value

: std logic vector(127 downto 0);

signal cipher_s, cipher_r

: std logic vector(127 downto 0);

attribute keep hierarchy : string;

attribute keep hierarchy of cipher arch 1 : architecture is "yes";

49

attribute equivalent register removal : string;

attribute equivalent_register_removal of cipher_r : signal is "no";

attribute equivalent_register_removal of cipher_s : signal is "no";

attribute keep : string;

attribute keep of round value

: signal is "true";

```

Virtual

analysis

Iterative Feeback

### **Pre-Silicon Security Evaluation**

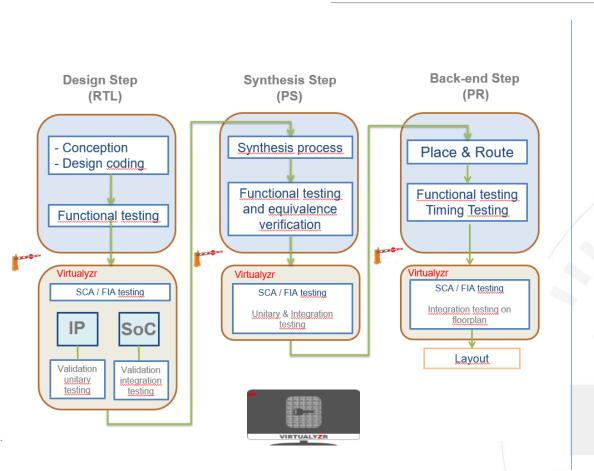

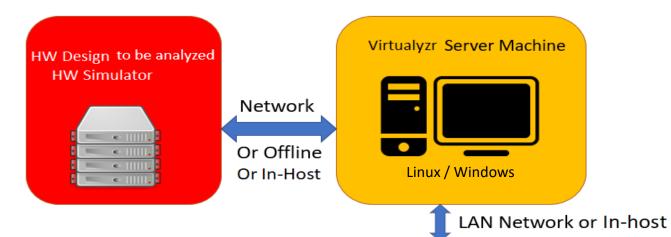

**■ Easy Integration to the Design Life-Cycle**

### Command Line User Interface for full automation

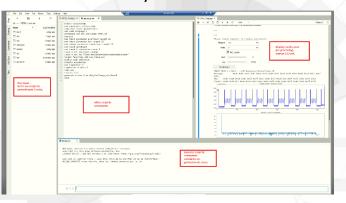

## Graphical User Interface for analysis build & test

### **Pre-Silicon Security Evaluation**

Easy Integration to the Design Life-Cycle

#### Mode 1: Build & Test

Browser-based interface

- · Build, live-test, modify, save and run

- Script and run all (CLI console)

#### Mode 2: Full Automation

SSH-based remote access to console

Full scripting

User 2

<sup>\*</sup> Or Multiple-users connexions

#### **Pre-Silicon Security Evaluation**

■ Snapshots (Build & Test interface)

# SECURE IC

#### **Pre-Silicon Security Evaluation**

#### **■ Your Gain**

- ✓ Provides a security verification layer: It runs hands-in-hands with functional verification workflow

- Compliance with ISO/IEC 17825, 20085 and evaluation standards CC, ISO/IEC 15408 and FIPS 140

- Detects, characterizes and extracts the security vulnerabilities from the design: IP and SoCs / cryptographic and non cryptographic targets / FPGA, ASIC, eFPGA

- Allows considering best analysis conditions (white box analysis, free noise, no jitter, etc).

- Allows performing security checkpoints at different design levels (behavioural level, netlist level)

- Allows checking countermeasures by fixing issues in masking scheme for instance: self-masking, variable time operation, simplification, etc.

- Allows more fidelity with the final technology

- The evaluation is cheaper as no measurement equipment or platforms are required.

- ✓ Improve and put forward the DFS (Design for security) approach.

### Pre-Silicon Security Evaluation

#### Differentiator Features

- Seamless flow from analysis of software, to mixed SW/HW, pure HW, netlist, GDSII, with the same interface

- ✓ Identification and characterization of security issues, annotated directly in the design as inputted by the user

- ✓ Simultaneous security and low power objectives /or security and safety (ISO 26262)

- ✓ Interactive API with the tool + full automation

- Latest distinguishers: collision, LRA, machine learning, etc.

- Delivered with many Use Cases on representative analyses, for a fast learning curve.

#### **THANKS** FOR YOUR ATTENTION

#### CONTACT

EUROPE APAC JAPAN AMERICAS sales-EU@secure-IC.com sales-APAC@secure-IC.com sales-JAPAN@secure-IC.com sales-US@secure-IC.com