# arm

# Acceleration and Differentiation for a World of a Trillion Devices

Mike Eftimakis – Director Business Innovation Strategy

3<sup>rd</sup> December 2019

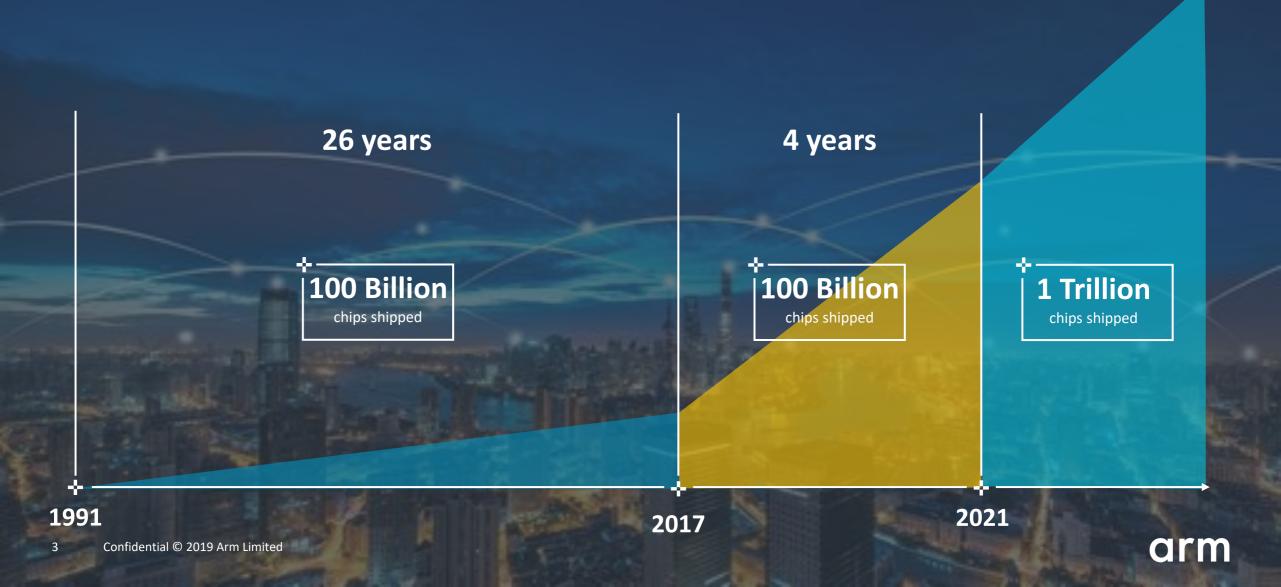

## Digital Transformation Drives Volume

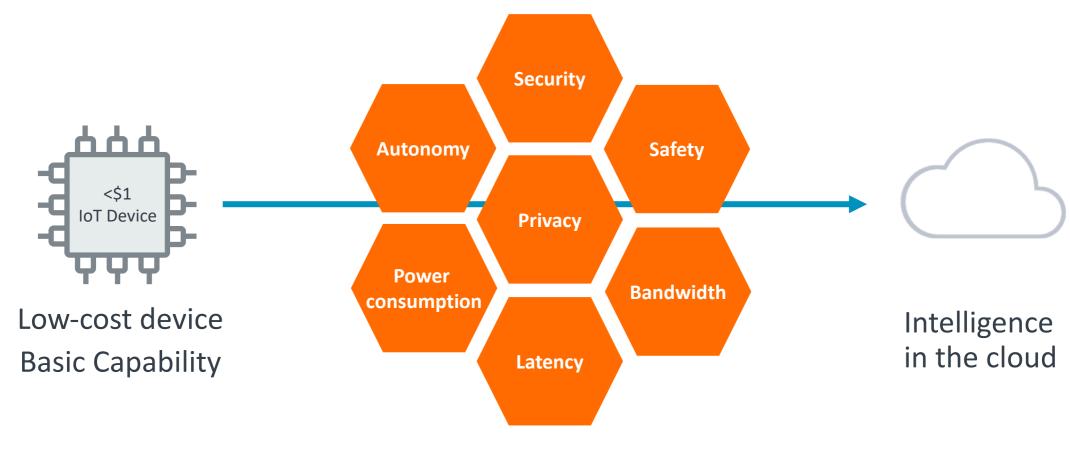

#### Barriers to IoT Mass Deployment

"All intelligence in the cloud" will struggle to scale

Barriers to deployment

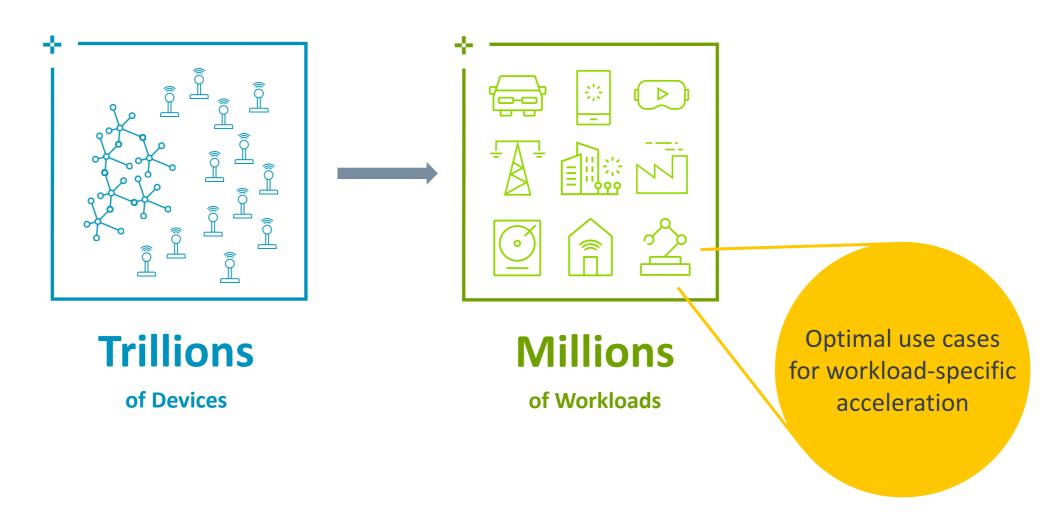

### Compute Requirements in a Trillion-device World

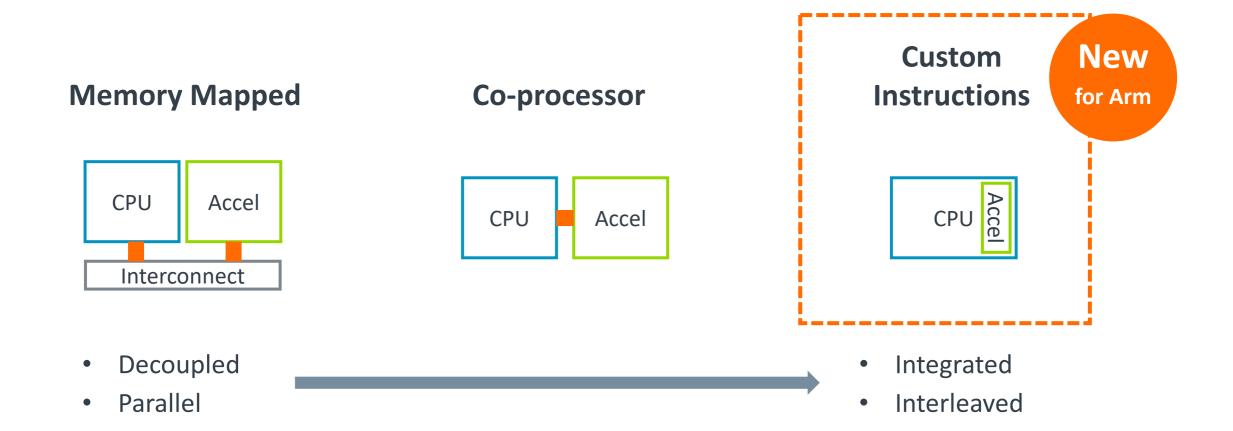

## Different Types of Acceleration

#### **Acceleration Through Custom Instructions**

```

r1, #0x5555555

mov.w

and.w

r1, r1, r0, lsr #1

r0, r0, r1

subs

r1, #0x33333333

mov.w

and.w

r1, r1, r0, lsr #2

bic

r0, r0, #0xccccccc

add

r0, r1

r1, #0x01010101

mov.w

add.w

r0, r0, r0, lsr #4

bic

r0, r0, #0xF0F0F0F0

muls

r0, r1, r0

1srs

r0, r0, #24

```

Multiple general-purpose instructions

```

MyOp01 p0, R1, #0

// pop count n R1, return r1

```

One instruction with custom logic

- Gain performance and efficiency

- Fewer cycles, less power

- Cost of more design investment

- Additional logic and integration

- Risk to hardware complexity and software ecosystem

- Impact on existing design re-verification

- Compilers and downstream tools need to support

#### The Benefits of Arm Custom Instructions

Lowest risk

Lowest cost path

to integrated custom

workload acceleration

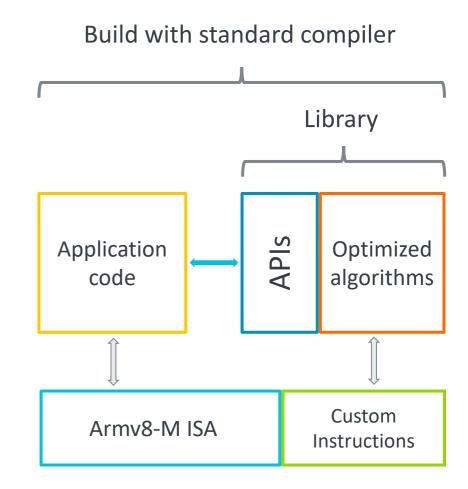

### **Customization without Software Fragmentation**

- Custom instructions use a pre-defined instruction space in Armv8-M

- Out-of-the-box support of Arm and 3<sup>rd</sup> party compilers and debuggers

- Custom instructions enabled through libraries shipped with standard board support package

#### **Arm Custom Instructions**

Workload-specific acceleration

- Available for Cortex-M33 CPU in 2020

No additional cost

- Standard for future Armv8-M processors

- Customization without software fragmentation

#### **Supported by Arm partners**

## arm

Thank You Danke Merci 谢谢 ありがとう Gracias Kiitos 감사합니다 धन्यवाद شکرًا תודה

The Arm trademarks featured in this presentation are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved. All other marks featured may be trademarks of their respective owners.

www.arm.com/company/policies/trademarks