## A Novel Event Based Image Sensor Architecture

#### M. AKRARAI<sup>1</sup> L. FESQUET<sup>2</sup> G. SICARD<sup>3</sup>

<sup>1</sup>University Grenoble Alpes, TIMA, Grenoble, France

<sup>2</sup>CNRS, TIMA, Grenoble, France

<sup>3</sup>CEA LETI, Grenoble, France

**IPSOC 2019**

< ロ > < 同 > < 回 > < 回 >

- Image sensors are present in various aspects of our life.

- Today we face the following challenges:

Power consumption, increasing resolution and frame rate. The last two, increase the resources required for image and video processing, a good example is **Automotive**.

How can we solve these engineering challenges?

Introduction of **frameless event based** image sensors and processing architectures:

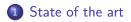

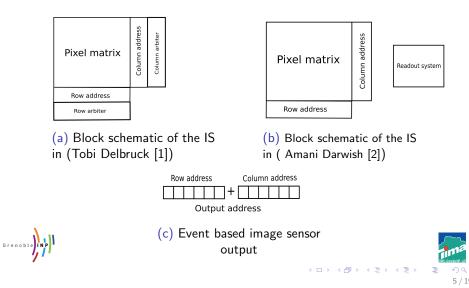

- Compression of temporal redundancy(Tobi Delbruck [2]).

- Compression of spacial redundancy (Amani Darwish[1]).

- Event-based Object Classification (Prophesee[3]).

< ロ > < 同 > < 回 > < 回 >

In both [2] and [1], the output of the image sensors is a **frameless** series of row and column addresses of active pixels:

(日) (四) (三) (三) (三)

6/19

## Can we combine spatial and temporal redundancies suppression and generate an event based processable output?

Grenoble

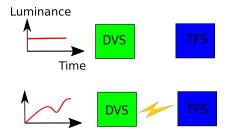

The combination of the two pixel (DVS, TFS) to harvest the benefits of both.

The TFS will measure absolute luminance only if the DVS pixel detects a change.

(b) Architecture B depicting 1 DVS per 3 TFS

(c) Architecture C depicting 1 DVS per 5 TFS

(d) Architecture D depicting 1 DVS per 8 TFS

Grenoble

(e) Architecture E depicting 1 DVS per 24 TFS

Figure : Suggested image sensor kernels

(b) Architecture B

Figure : Example of pixel matrix of architecture A and B

To form the image sensor matrix, the kernel is repeated until we reach the desired resolution.

| Scenario | Dimensions     | Frame rate | DVS thresholds |

|----------|----------------|------------|----------------|

| Highway  | 1200 	imes 600 | 30 fps     | 1,5,10 %       |

| Parking  | 1200 	imes 600 | 30 fps     | 1,5,10 %       |

Worst case, will be detecting all the events from the input videos for 10 seconds:

$1200\times 600\times 30\times 10=216000000\textit{Events}$

イロト イポト イヨト イヨト

(a) Highway scenario: car on the (b) Parking scenario: a man walks in road the front of a car

Figure : The two simulation scenarios

#### Parking scene

(a) Original highway scene

Highway.mp4

parking.mp4

(b) Original parking scene

(c) Simulation output video for architecture B, 5 % DVS threshold, Highway scenario

(d) Simulation output video for architecture B, 5 % DVS threshold, Parking scenario

< ロ > < 同 > < 回 > < 回 >

Grenoble INP

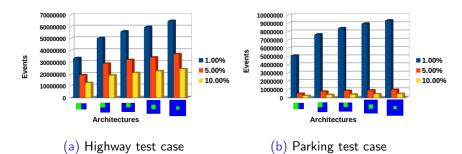

Figure : The number of generated events per architecture and DVS threshold

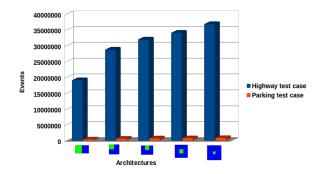

Figure : Comparison of architectures activity per test case for 5 % DVS threshold

#### Conclusion

The simulation results confirm that achieving complete redundancies suppression is possible, while maintaining the relevant information of the scene.

#### Upcoming work

One of the presented architectures will be implemented in 28 nm FDSOI technology to provide the first proof of concept.

## References I

- "A 128×128 120 dB 15µs Latency Asynchronous Temporal Contrast Vision Sensor" P. Lichtsteiner and C. Posch and T. Delbruck, Journal, IEEE Journal of Solid-State Circuits, 2008

- A. Darwish, L. M. G. Rocha, L. Fesquet and G. Sicard, "Design of a fully asynchronous image sensor reading system," 2015 Conference on Design of Circuits and Integrated Systems (DCIS), Estoril, 2015, pp. 1-5.

- Sironi, Amos & Brambilla, Manuele & Bourdis, Nicolas & Lagorce, Xavier & Benosman, Ryad. (2018). HATS: Histograms of Averaged Time Surfaces for Robust Event-based Object Classification.

< ロ > < 同 > < 回 > < 回 >

## This work has been partially supported by the OCEAN12 project (H2020-EU.2.1.1.7 no78327)

# THANK YOU