#### Sowmyan Rajagopalan, Founder & CTO

**Thalia Design Automation**

Bluetooth IP Migration & Leveraging FDSOI Back Gate Biasing feature December, 2019

## **Analog IP Design – Decision fork**

#### Design new IPs

- Address new sections of the market

- Increasing revenue

- Targeted customer base

- Exciting

#### Build a portfolio of analog IPs

Expand within the existing market Stabilise Increase revenue – widen the customer base

#### Not an Either-Or Situation

2 9 December 2019

# Analog IP Reuse – Is it a myth ?

- Analog circuit design is impacted by a number of factor

- Device performance,

- Technology characteristics,

- Functional requirements,

- Design methodology

- Migrating an Analog circuit into a reduction of an existing IP custom requirements

- Even a bandgap requires des on edo !!!

- Limited solutions in market and a shortage of good analog designers exacerbates the problem

- Is efficient Analog IP reuse a myth/dream ?

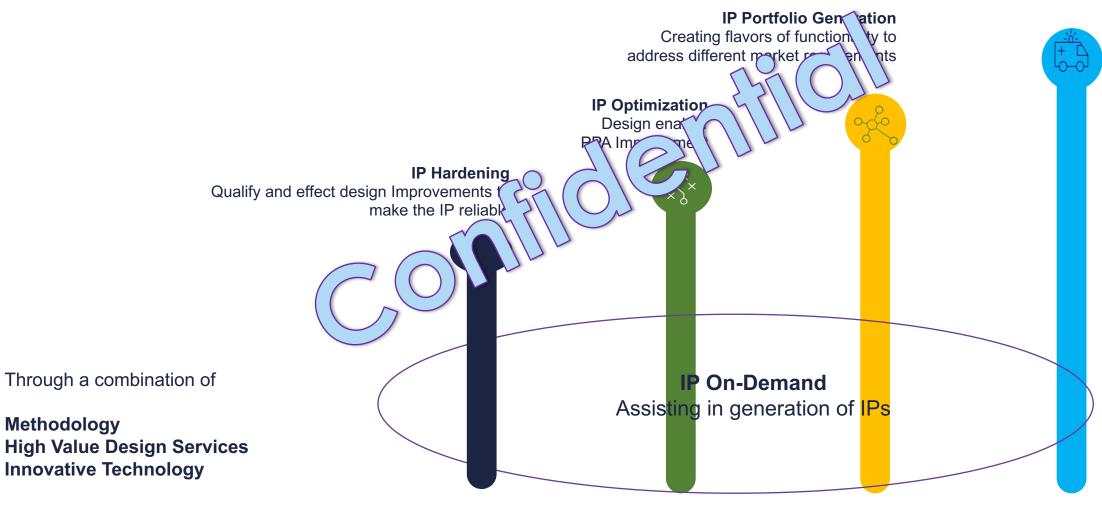

## Thalia – Who are we ?

- Paradigm shift in how Analog IP is reused

- Thalia's unique Re-use Platform as-a-Service (Peral)

- allows analog IP vendors to diversify their product r

- optimize performance of new and existing IP;

- and to quickly and efficiently serve man at a downatever their customers' choice of process technology.

- RePaaS addresses costomers analog and mixed signal design requirements by combining three sleptents – The Trifecta :

- proprietary design automation technology that increases designer efficiency and improves quality of results;

- innovative design methodology a design based approach rather than a CAD based or circuit synthesis;

- and an experienced team with proven expertise in RF, analog and mixed signal design

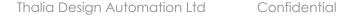

### Thalia Value Proposition

IP Migration Migrating Design across technologies

## **Thalia Unique Selling Point**

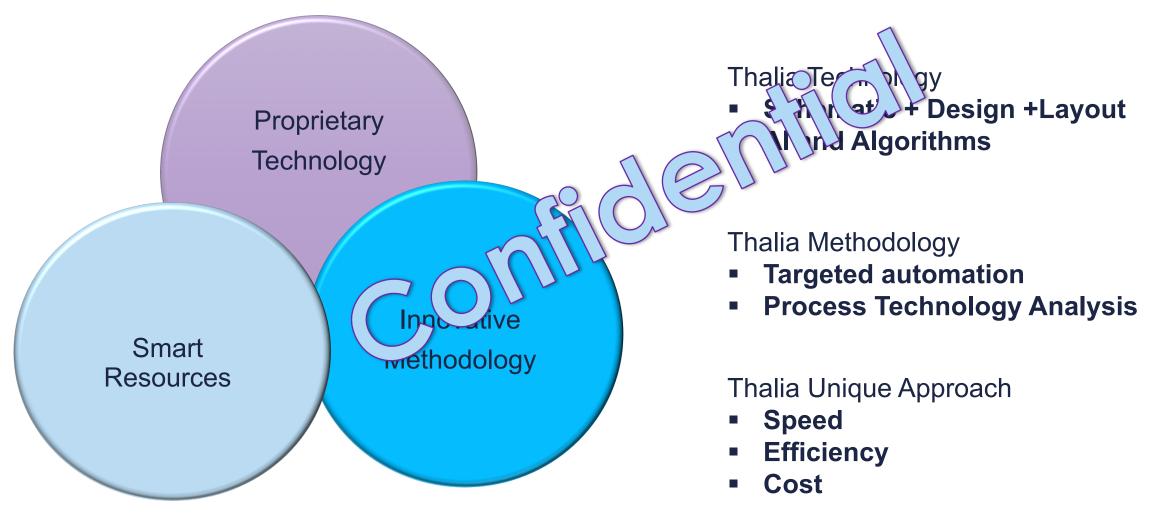

# Amalia<sup>™</sup> Technology

## **Automated Process Technology Analysis**

- A design centric ap row h

- Mapping based not only on parameter names/values or callback limits

- Device level simulations to match Ft, Vth, gm, gm/ld, Vds-lds curves and other second order effects

- Circuits similar to base design post migration, comparable performance and hence lesser design iterations

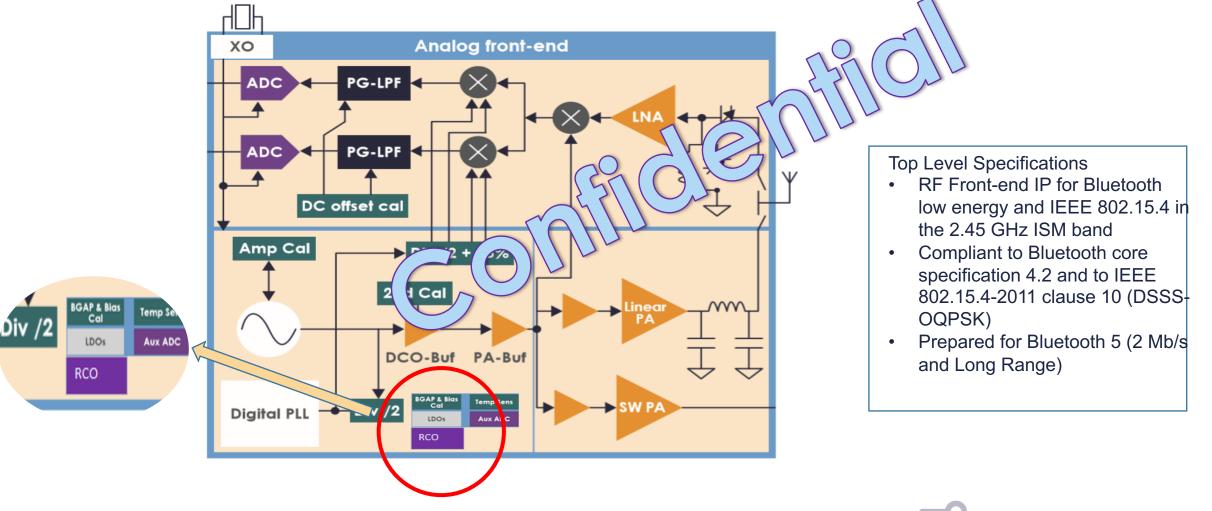

## **Bluetooth IP Reuse & FDSOI Techniques**

10 |

9 December 2019

Confidential

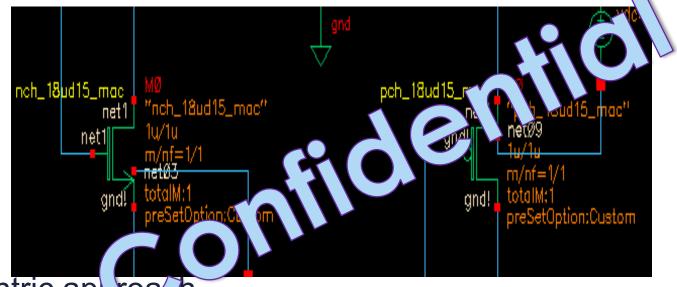

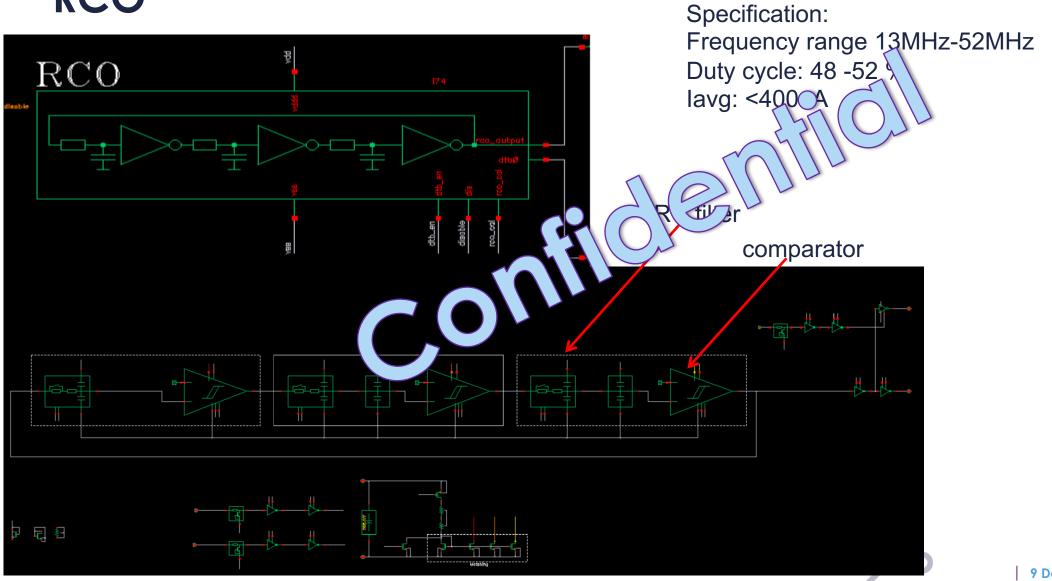

RCO

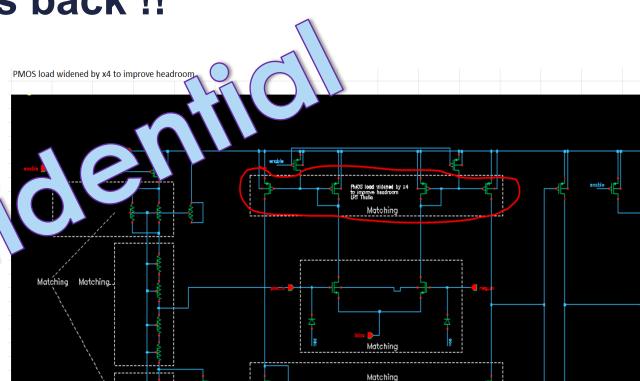

## **Process differences strikes back !!**

- Vt of the nfet and pfet between the technologies were different

- Headroom pressure

- To maintain the required drive, the W of mirrors had to be increased (and L). Increased area

- So flipwell lvtfets were used and Vsb altered to reduce the

# **Design Example: RCO – Thalia's Solution**

Targeted automation to provide incremental time and cost savings – full automation doesn't work in Analog

13 9 December 2019

## **Business Value: Analog Migration**

|      | Parameter<br>Vdd<br>temperature<br>topinclude.scs | Nominal<br>900m<br>27<br>top_tt |             |        |                  |                      |          |       | 5                                  | 51(                                   | O)/         | 7      |           |           |           |

|------|---------------------------------------------------|---------------------------------|-------------|--------|------------------|----------------------|----------|-------|------------------------------------|---------------------------------------|-------------|--------|-----------|-----------|-----------|

| Test | Output                                            | Nominal                         | Spec        | Weight | Pass/Fail        | Min                  | Max      |       |                                    | ) ) ) ) ) ) ) ) ) ) ) ) ) ) ) ) ) ) ) |             |        |           |           |           |

| PVT  | i_avg                                             | 245.7 uA                        | < 500       |        | pass             | 119.8 uA             | 411.6 uA | ~     |                                    | UUU                                   |             |        |           |           |           |

| PVT  | Duty Cycle Freq_low                               | 50.43 %                         | range 40 60 |        | pass             | 47.82 %              | 51.5 %   |       | $( \bigcirc ) \setminus \setminus$ | 1                                     |             |        |           |           |           |

| PVT  | Duty Cycle Freq_high                              | 49.51 %                         | range 40 60 |        | pass             | 46.97 %              | 50.75 %  | _A \_ | Pmeter                             | Nominal                               |             |        |           |           |           |

| PVT  | Frequency_Comp_f_high                             | 26 MHz                          | range 13 52 |        | pass             | 15.83 MHz            | ()MHz    |       | Vdd                                | 900m                                  |             |        |           |           |           |

| PVT  | Frequency_Comp_f_low                              | 15.18                           |             |        |                  | 9.235                | GAL      |       | temperature                        | 27                                    |             |        |           |           |           |

| PVT  | Startup time                                      | 29.94 ns                        | < 50        |        | pass             | 0 ns 👌               |          |       | topinclude.scs                     | top_tt                                |             |        |           |           |           |

|      |                                                   |                                 |             |        |                  |                      | 111      | Test  | Output                             | Nominal                               | Spec        | Weight | Pass/Fail | Min       | Max       |

|      |                                                   |                                 |             |        |                  | $ \land \land \land$ | 1-       | PVT   | i_avg                              | 240.3 uA                              | < 500       |        | pass      | 102.5 uA  | 414.2 uA  |

|      |                                                   |                                 |             | $\sim$ | $\left( \right)$ |                      |          | PVT   | Duty Cycle Freq_low                | 50.66 %                               | range 40 60 |        | pass      | 49.8 %    | 50.83 %   |

|      |                                                   |                                 |             |        |                  |                      |          | PVT   | Duty Cycle Freq_high               | 50.05 %                               | range 40 60 |        | pass      | 48.34 %   | 50.05 %   |

|      |                                                   |                                 | (           |        |                  |                      |          | PVT   | Frequency_Comp_f_high              | 26.95 MHz                             | range 13 52 |        | pass      | 15.29 MHz | 42.33 MHz |

|      |                                                   |                                 |             |        | 7 -              |                      |          | PVT   | Frequency_Comp_f_low               | 15.52                                 | -           |        |           | 9.387     | 24.56     |

|      |                                                   |                                 |             |        |                  |                      |          | PVT   | Startup time                       | 16.79 ns                              | < 50        |        | pass      | 10.47 ns  | 33.02 ns  |

- The circuit was migrated, simulated, design tweak applied and laid out.

- Design expertise along with Design methodology allowed Thalia to identify the right component

1

## **Rapid Analog Porting - Reuse Customer Examples**

| Classification        | Examples                 | Redesir n<br>Cycle Tir     | Thalia's<br>Cycle Time*      |  |  |

|-----------------------|--------------------------|----------------------------|------------------------------|--|--|

| Standard Analog IP    | DAC, ADC, PLL            | 12-1 W PK<br>3 TEJ**       | 4-8 weeks<br>[2 FTE]**       |  |  |

| Application Analog IP | Bluetooth,<br>GPS/GLONAL |                            | 18-22 weeks<br>[~ 6-7 FTE]** |  |  |

| Application Analog IP | Du on WLN                | >50 weeks<br>[~ 6-8 FTE]** | 22-28 weeks<br>[~ 6-7 FTE]** |  |  |

(\*) Elasped calendar time to Specification Compliant Design

(\*\*) FTE : Full Time Equivalent

Timescales will be impacted by Circuit complexity and process node differences

# **Customer Testimonial**

### Kave Kianush, Catena Vice President and Chief Technology Officer

- "We're taking a new approach, which represents a fundamental shift in the way analog IP is created and delivered.

- Our relationship with Thalia helps us to deliver exactly the right feature and performance combination for our customers, against ever more demanding time-tomarket and cost requirements.

- Thalia's combination of novel design automation technology and analog design expertise is unique in the market.

- We've already seen a positive impact on our ability to deliver against tight customer deadlines."

- <u>https://www.thalia-da.com/catena-selects-thalia-da-to-facilitate-analog-ip-re-use/</u>

## **Summary: Re-inventing Analog Reuse**

- RePaaS A platform that delivers efficient reuse of Analog IP

- Unique combination of Technology, Methodology and Design experience

- Reduced design cycle time and hence lower cost -> up to 50% time and cost savings

- Proven track record 22nm to 350nm; Samsung, TSMC, UMC, GF, Tower, SMIC, AMS, Tier 1 Technologies

- Direct application in migrating IPs Off the shelf IPs

Contact us sales@thalia-da.com