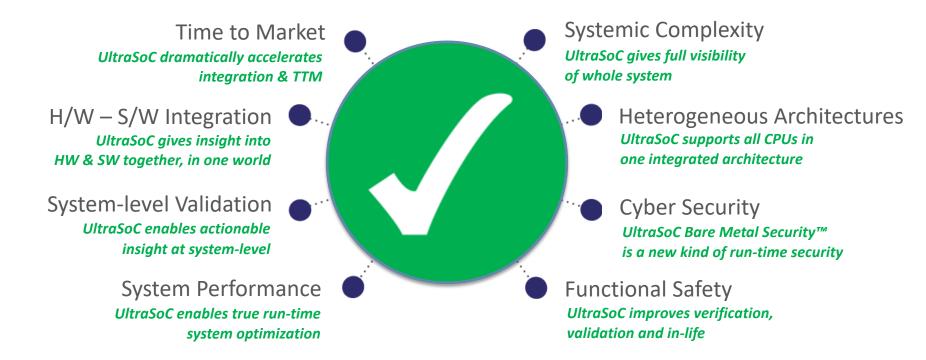

Value Proposition

**Architectural Overview**

# **Corporate Overview**

- VC-funded, Cambridge UK

- Restart 2015

- £4.7M round May '17

- New Chairman Alberto Sangiovanni-Vincentelli

- 25 patents granted + 16 pending

- Seasoned management team

- Key partners & ecosystem

- Proven technology, proven product-market fit

- Revenue, blue-chip customers, repeat business

C.SKY Alibaba

**FAANG** Data centre

Value Proposition

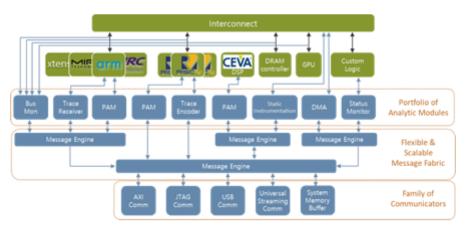

**Architectural Overview**

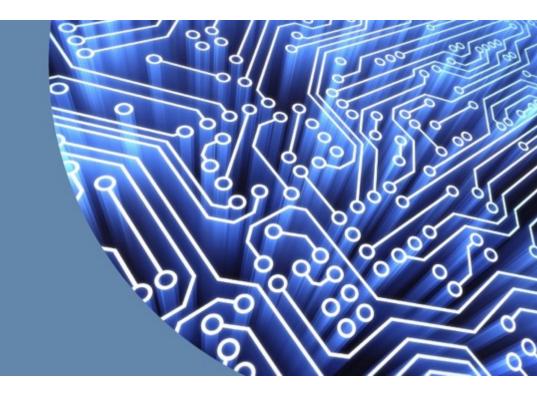

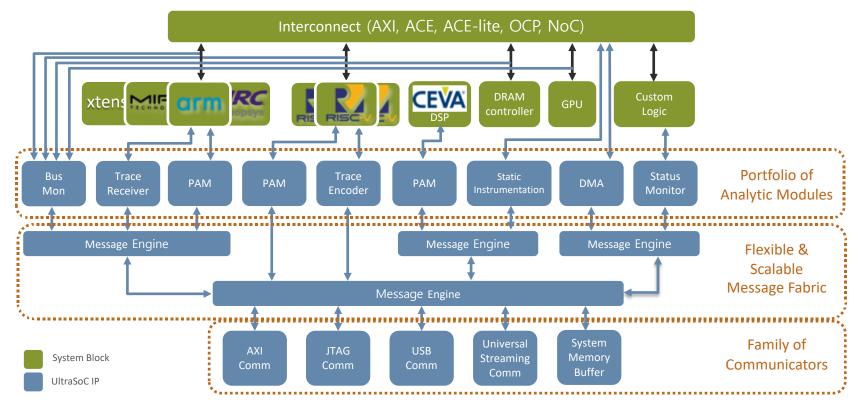

#### UltraSoC: on-chip Analytics for SoC as a Whole

#### A coherent architecture to debug, develop, optimize & secure

- Full SoC visibility, HW & SW

- Support all architectures: Freedom of IP selection

- Real-time & non-intrusive

- Advanced analytics & forensics

- Power/Performance optimization

- "in life" analytics & SLA compliance

- Supports Functional Safety

- Supports Bare Metal Security™

- High-speed debug over USB or SerDes

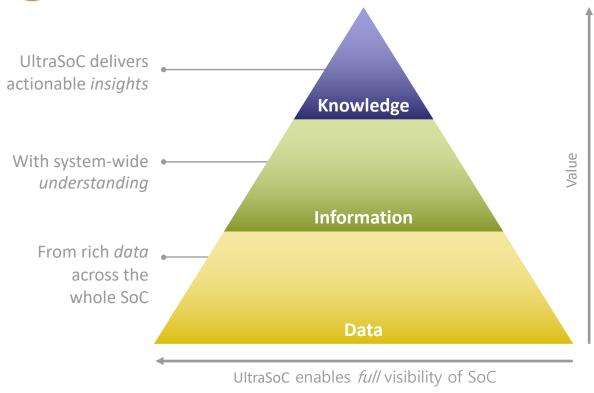

# Actionable Insights across the whole SoC

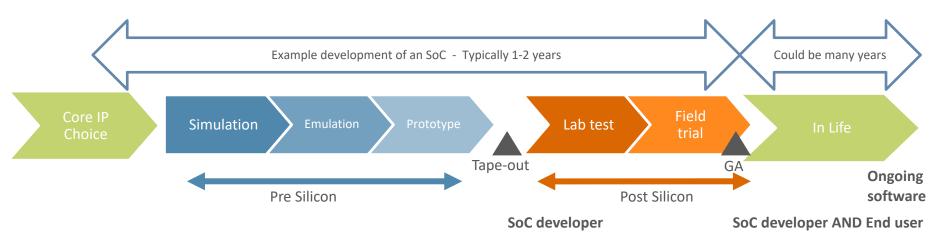

#### In development – and beyond

...supports all cores, reducing lock-in, increasing flexibility

# ultrasoc

...is integrated with the leading simulation and emulation tools

Adds value to emulation & prototyping, accelerates development

# ultrasoc

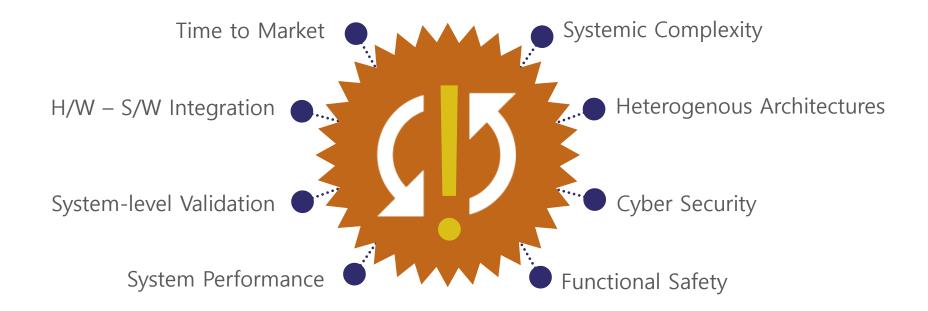

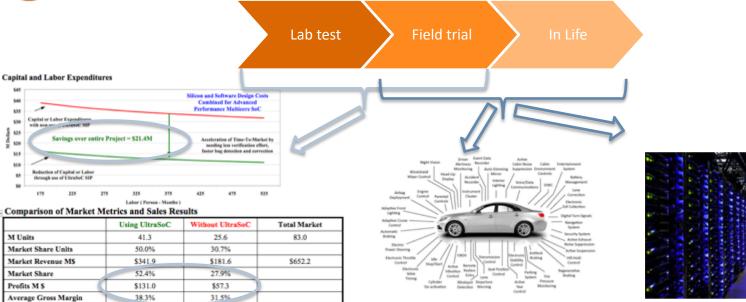

...radically improves:

- Time-to-revenue

- Quality / Safety

- Profits due to faster time to market

...detects anomalies:

- optimization, security and functional safety

- Non intrusive

Breakeven M Units

Aggregate ASP

#### UltraSoC creates value both in-lab and in-life

UltraSoC accelerates innovation and maximizes profitability

7.6

\$8.28

Faster TTM, higher quality, lower cost & higher margin

14.3

\$7,17

Over entire product life

UltraSoC **detects threats** and hazards an order of magnitude faster than any other solution – radically increasing security and safety UltraSoC allows rapid **optimization of application SW**: improving performance, reducing TCO

Value Proposition

Architectural Overview

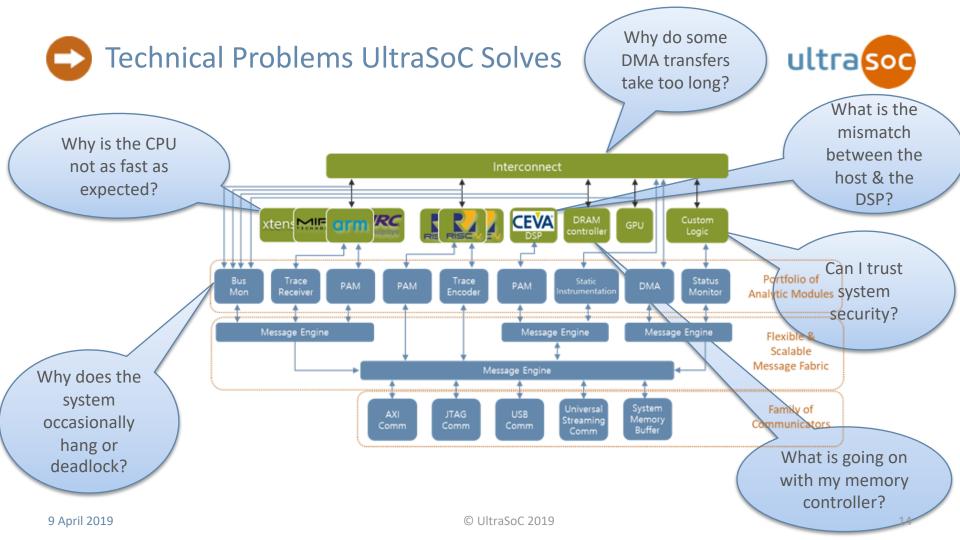

### Advanced Debug/Monitoring for the Whole SoC

### Software tools for data-driven insights

# Third Party Tool **Vendor Partnerships** UltraDevelop interfaces with almost all common validation and verification solutions: arm cadence CEVA eclipse **LAUTERBACH** SYNOPSYS\* **imperas** TELEDYNE LECROY Everywhereyoulook"

#### UltraSoC is a modular IP platform

[Representative # of gates]

ANALYTIC

Direct interface to CPU or DSP to control core and access rich debug information

Protocol-aware analysis of complex interconnects, master or slave, with smart filtering

Status Monitor [11k]

Non-intrusively monitor custom logic or IP blocks (GPU, security etc.)

MESSAGE

Message Infrastructure [8k per Message Engine]

Provides message routing, buffering and event distribution for triggering

COMMUNICATORS

PHY and requiring no software

JTAG [20k]

Industry-standard IEEE 1149.1 interface

Directly store data in system memory for analysis

Universal Streaming [20k]

A range of serial links, including SWD and SerDes

+ 20 additional modules

Total area overhead is typically ~1%

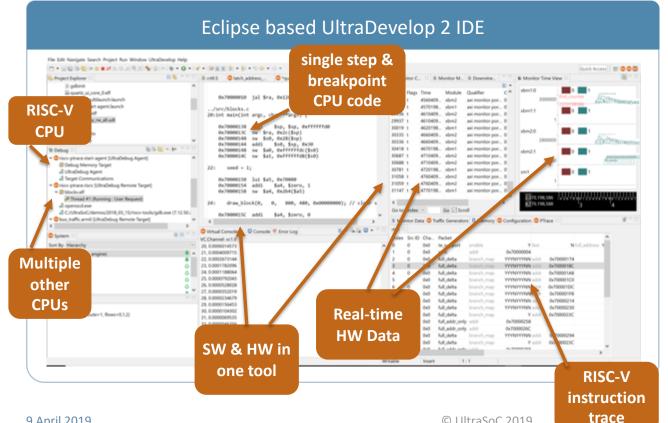

# Strategic changes in the market - RISC-V

- UltraSoC has the only commercial development environment for RISC-V

- Includes run control and trace (inst and data)

- Heterogeneous, massively multicore

- FPGA demonstrator, Eclipse IDE (gdb, gcc, openOCD, Imperas MPD)

- Silicon proven solution

- Partnerships with leading core vendors

- RISC-V Foundation member since 2016

- Chair of trace group, member/contributor debug group

16

Value Proposition

Architectural Overview

| Non-intrusive                                                                        | Debug does not impact/degrade system performance                                                                                                                                  |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "Smart" monitors                                                                     | Detect items of interest in hardware, at wire-speed Massively reduce trace bandwidth & memory Home in on problems efficiently Not necessary to post-process large volumes of data |

| Protocol-aware bus monitors (AXI, ACE, ACE-Lite, OCP, OCP 2.0, CHI etc)              | Identify specific transactions; easily spot problems                                                                                                                              |

| Full support for all standard processors (ARM, RISC-V, MIPS, Xtensa, Arc, CEVA, etc) | Uniquely supports heterogeneous architectures; "mix & match" across vendors; fix hardware, software or HW+SW integration                                                          |

| Message-based protocol                                                               | Easy to place & route; extensible & versatile; allows local processor for "autonomous" control in the field                                                                       |

| Powerful status monitor                                                              | Configurable smart logic analyzer for custom logic                                                                                                                                |

| Secure                                                                               | Powerful security architecture                                                                                                                                                    |

#### **UltraSoC Analytics, Monitoring & Security**

- The only commercial heterogeneous solution

- The only commercially available Trace and Debug solution for Risc-V

- Non-intrusive, wire-speed monitors

- Integration Simplicity

- High-speed debug over USB or SerDes

- Enables faster debug, forensics, optimization

- pre-silicon & post-silicon

- Enables in-life monitoring

- reliability, compliance & Bare-Metal Security™

Contact details:

John Hartley- UltraSoC VP Global Sales

john.hartley@ultrasoc.com www.ultrasoc.com

**y** @UltraSoC