#### Sowmyan Rajagopalan, Founder & CTO

Thalia Design Automation

Is efficient Analog IP reuse a Myth?

An Innovative Approach to make Analog IP reuse a reality

April, 2019

#### Analog IP Reuse – Why is it difficult?

- Analog circuit design is impacted by a number of factors

- Device performance,

- Technology characteristics,

- Functional requirements,

- Design methodology

- Migrating an Analog circuit into a new technology is almost a redesign of an existing IP – custom requirements

- Even a bandgap requires design redo !!!

- Limited solutions in the market and a shortage of analog designers exacerbates the problem

- Is efficient Analog IP reuse a dream?

2 | 17 April 2019

#### Thalia at a glance

2015

Solutions Offering launched targeting Analog Reuse

•Experienced Delivery Team Established – Avg. 20 years of experience 2017

Thalia established in India

2018

Thalia expanded to Germany

Amalia™ Suite Initial release

2014

Several customer designs delivered

•RF Front end, Baseband applications

2016

Amalia<sup>TM</sup> expanded to address several flavors of TSMC, GF, UMC, In-house technologies of Tier1 design companies

2017

2017

Thalia Design Automation Ltd

Confidential

17 April 2019

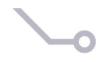

#### Thalia's target solutions

Thalia Design Automation Ltd

Through a combination of

**Innovative Technology**

Methodology

Confidential

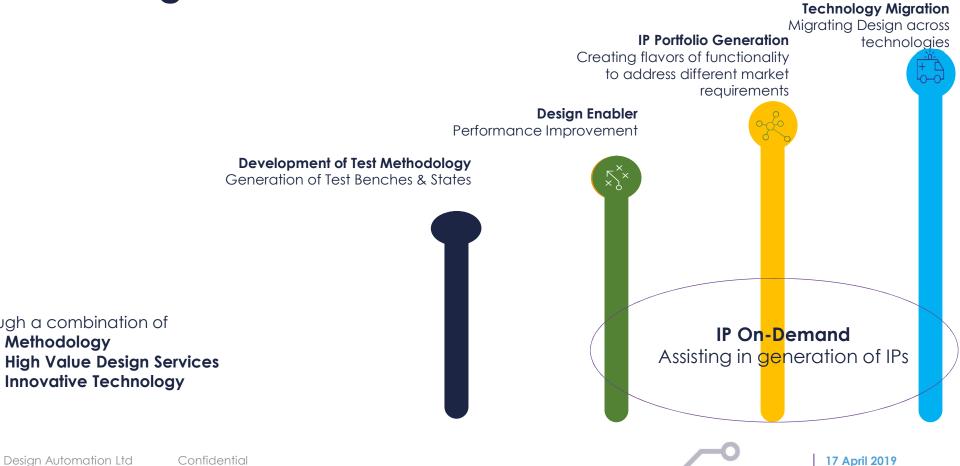

### Why are we different?

Thalia Unique Approach

- Speed

- Efficiency

- Cost

Thalia Resources

> 20 Years experience

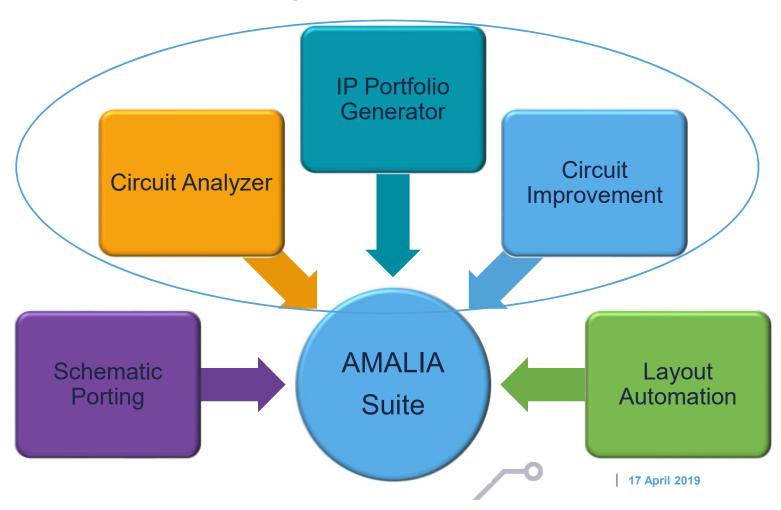

# **Toolsets Amalia<sup>™</sup> Capability**

**Design Enabling Capability**

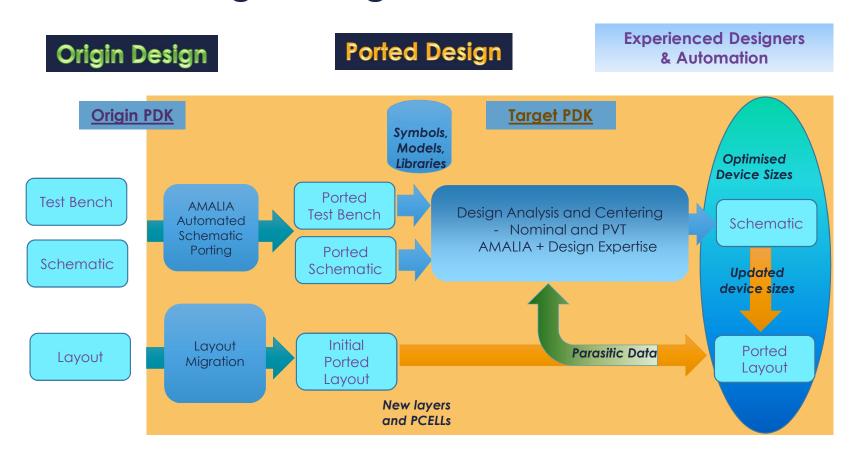

#### Thalia's Analog Porting Flow

Thalia Design Automation Ltd Confidential 7 17 April 2019

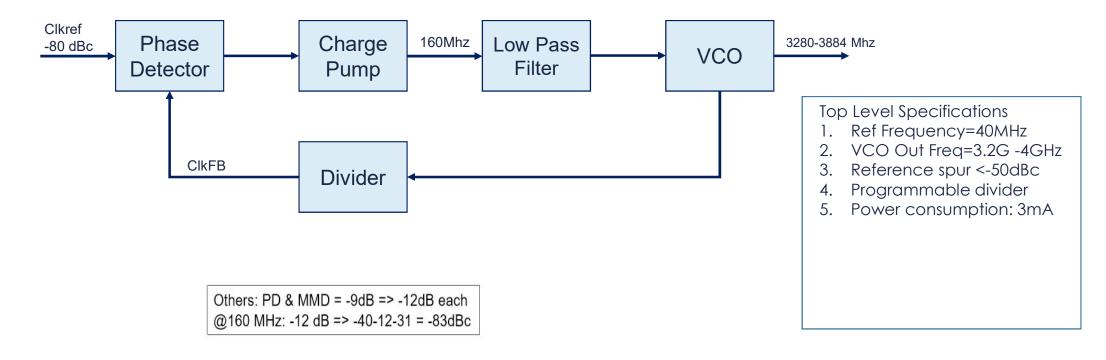

### Design Example – PLL Application in Wi-Fi Migration

Thalia Design Automation Ltd

Confidential

8

17 April 2019

#### The Design Conundrum

| VCO(LC based)                    |                        | Programmable Feedback divider |         |                       | Phase Frequency Detector |                          |       |  |

|----------------------------------|------------------------|-------------------------------|---------|-----------------------|--------------------------|--------------------------|-------|--|

| Centre frequency                 | 3.86GHz                | Opera Schedule 6.4GHz freque  |         | •                     | perating Up to 1 equency |                          | 60MHz |  |

| Current consumption              | 1.5mA                  | Current consumption           | T.0mA   |                       |                          |                          |       |  |

| Tuning range with band selection | 3GHz-4GH               | Output swing                  | Rail to | Full different        |                          | e Pump<br>40uA-200       | υA    |  |

| Phase noise                      | -120dBc/H<br>@1MHz off | >                             | •       | design with programmo |                          |                          |       |  |

| Topology                         |                        |                               |         |                       |                          | echnology<br>Differences |       |  |

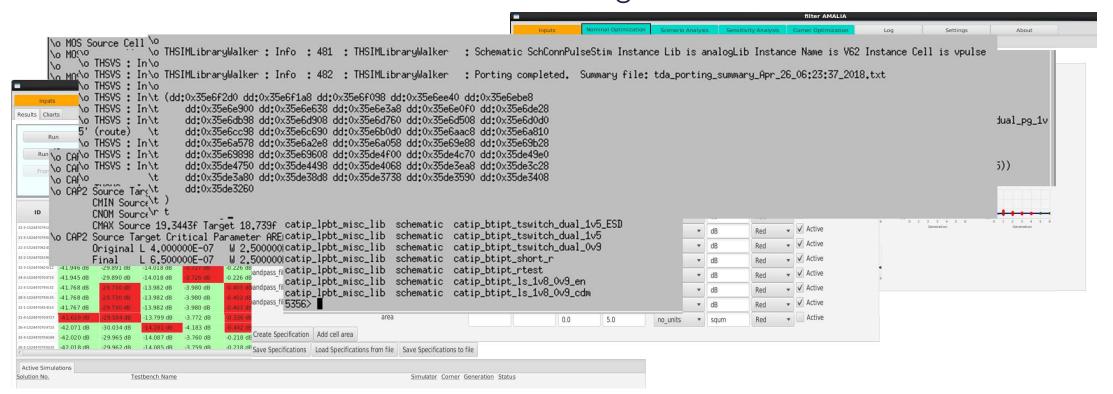

#### Design Example: Clk PLL – Thalia's Solution

Targeted automation to provide incremental time and cost savings – full automation doesn't work in Analog

Thalia Design Automation Ltd Confidential 10 | 17 April 2019

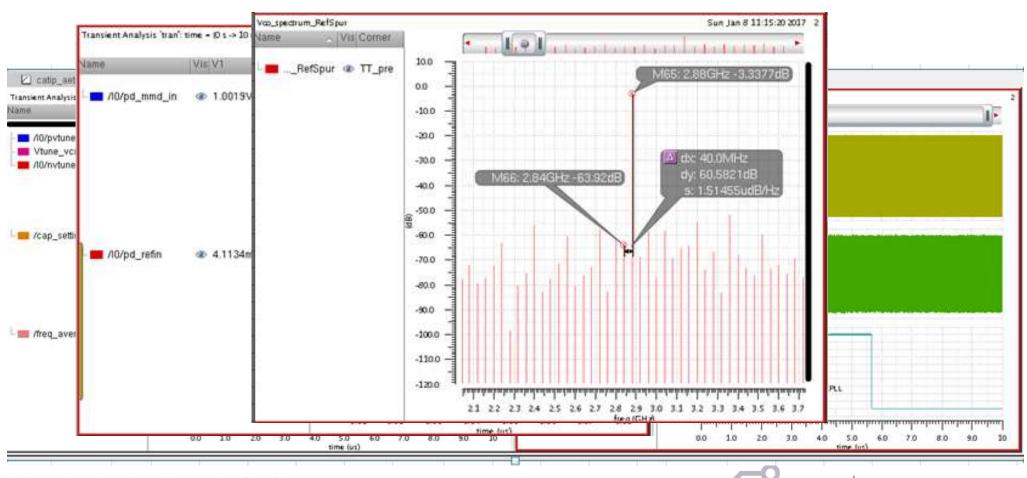

# Design Example: CLK PLL – Migration Results

Thalia Design Automation Ltd

Confidential

11 | 17 April 2019

#### **Business Value: Analog Migration**

| Design  | Parameter                                                   |                                                            | Verified Specification |       |     | Min | Тур   | Max | Units |

|---------|-------------------------------------------------------------|------------------------------------------------------------|------------------------|-------|-----|-----|-------|-----|-------|

|         | Conditions                                                  |                                                            | min                    | nom   | max |     |       |     |       |

|         | Functional requirements                                     |                                                            |                        |       |     |     |       |     |       |

| CLK-PLL | PLL comparison<br>frequency                                 | Same as the XO<br>frequency                                |                        | 40    |     |     | 40    |     | MHz   |

|         | Output frequencies to<br>the LB and HB PLL:s<br>(low noise) |                                                            |                        | 160   |     |     | 160   |     | MHz   |

|         |                                                             | To frequency counter                                       |                        | 40    |     |     | 40    |     | MHz   |

|         | Other output                                                |                                                            |                        | 960   | Ī   |     | 960   |     | MHz   |

|         | frequencies                                                 | Test-output                                                |                        | 40    |     |     | 40    |     | MHz   |

|         |                                                             | To ADC/DAC                                                 |                        | 160   |     |     | 160   |     | MHz   |

|         | Parametric<br>requirements                                  |                                                            |                        |       |     |     |       |     |       |

|         | EVM from Integrated<br>phase noise at the<br>160MHz output  | Integrated from 10kHz<br>to 2MHz and referred<br>to 5.9GHz | ?                      | -42.9 |     |     | -43.6 |     | dB    |

|         |                                                             |                                                            |                        |       |     |     |       |     |       |

- Ref Frequency=40MHz

- Clock output: 2.88GHz

- VCO phase noise =-121dBc/Hz @1MHZ.

- Programmable loop filter AND Programmable divider.

- EVM for Integrated PHASE NOISE @160MHZ should be better than -42dB.

- Ref spur =-90dB

- TSMC to GF 28nm

- Migrated, Design changes and layout in < 6-7 weeks

Thalia Design Automation Ltd

Confidential

## Solutions delivered by Thalia

#### Unique combination of Experienced Resources and Innovative Technologies

| Application           | Technologies                                 | Nodes                        |  |  |

|-----------------------|----------------------------------------------|------------------------------|--|--|

| Dual Band WIFI        | TSMC, GF, Samsung                            | 22nm, 28nm, 40nm, 28nm FDSOI |  |  |

| Bluetooth IP          | TSMC, GF, Samsung                            | 28nm, 40nm 28nm FDSOI        |  |  |

| ADCs, PLLs, LNAs, PAs | TSMC, GF, Tier 1 In-house technologies, SMIC | 16FF to 130nm                |  |  |

| PMIC Derivatives      | TSMC, GF, UMC, AMS                           | 16FF to 350nm                |  |  |

Wide range of Technologies and nodes from 350nm down to 16FF nm Proven Track Record delivering designs in cutting edge applications and in newest technologies

## Rapid Analog Porting - Reuse Customer Examples

| Classification        | Examples                  | Redesign<br>Cycle Time*       | Thalia's<br>Cycle Time*      |

|-----------------------|---------------------------|-------------------------------|------------------------------|

| Standard Analog IP    | DAC, ADC, PLL             | 12-16 weeks<br>[2-3 FTE]**    | 4-8 weeks<br>[2 FTE]**       |

| Application Analog IP | Bluetooth,<br>GPS/GLONASS | >40-50 weeks<br>[~ 6-8 FTE]** | 18-22 weeks<br>[~ 6-7 FTE]** |

| Application Analog IP | Dual Band WLAN            | >50 weeks<br>[~ 6-8 FTE]**    | 22-28 weeks<br>[~ 6-7 FTE]** |

(\*) Elasped calendar time to Specification Compliant Design

(\*\*) FTE: Full Time Equivalent

Timescales will be impacted by Circuit complexity and process node differences

#### **Customer Testimonial**

#### Kave Kianush, Catena Vice President and Chief Technology Officer

"We're taking a new approach, which represents a fundamental shift in the way analog IP is created and delivered.

Our relationship with Thalia helps us to deliver exactly the right feature and performance combination for our customers, against ever more demanding time-to-market and cost requirements.

Thalia's combination of novel design automation technology and analog design expertise is unique in the market.

We've already seen a positive impact on our ability to deliver against tight customer deadlines."

https://www.thalia-da.com/catena-selects-thalia-da-to-facilitate-analog-ip-re-use/

Thalia Design Automation Ltd Confidential | 17 April 2019

#### Summary: Re-inventing Analog Reuse

- Unique combination of toolsets, methodology and design experience

- Proven track record 16 FF to 350nm; TSMC, UMC, GF, Tower, SMIC, AMS, Tier 1 Technologies

- Direct application in migrating IPs Off the shelf IPs

Contact us sales@thalia-da.com

16 | 17 April 2019