## The environmental footprint of semiconductor manufacturing

Cédric Rolin

Program Manager, Sustainable Semiconductor Technologies & Systems

DATE conference, April 17, 2023, 14:40 Workshop 01: Eco-ES: Eco-design and circular economy of Electronic Systems

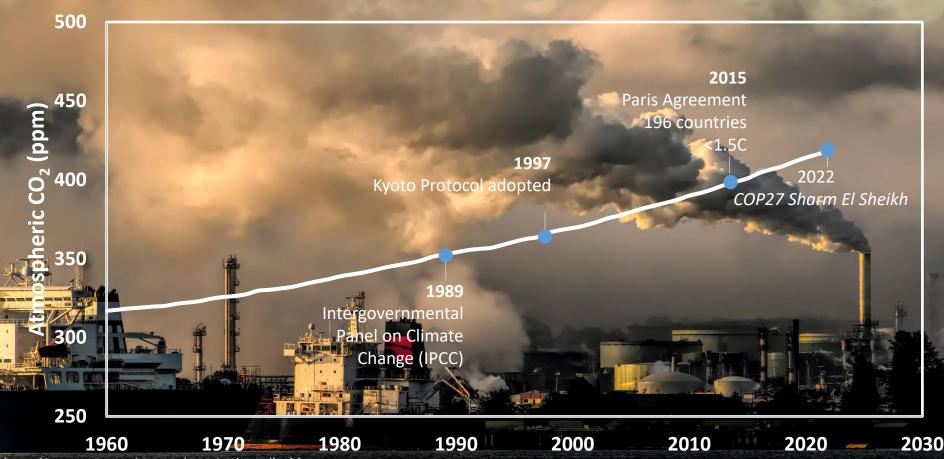

# CO<sub>2</sub> in the atmosphere increases despite global commitments

https://www.noaa.gov/news-release/carbon-dioxide-now-more-than-50-higher-than-pre-industrial-levels

Photo by Chris LeBoutillier on Unsplash

Scripps CO2 Program, 2222

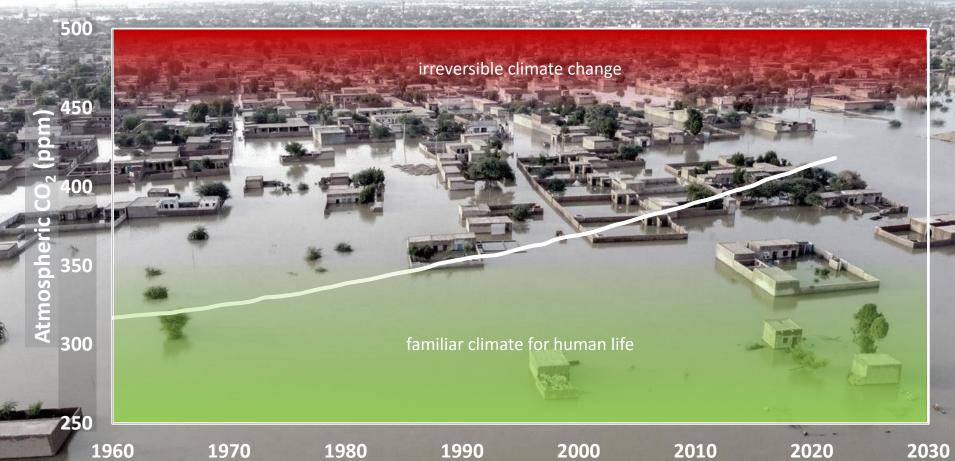

# Need to address emissions, not simply make commitments

Solomon et al., Irreversible climate change due to carbon dioxide emissions, PNAS 2009

Pakistan giant monsoon, Summer 2022 Photo by Fida Hussain/AFP

Scripps CO2 Program, 2222

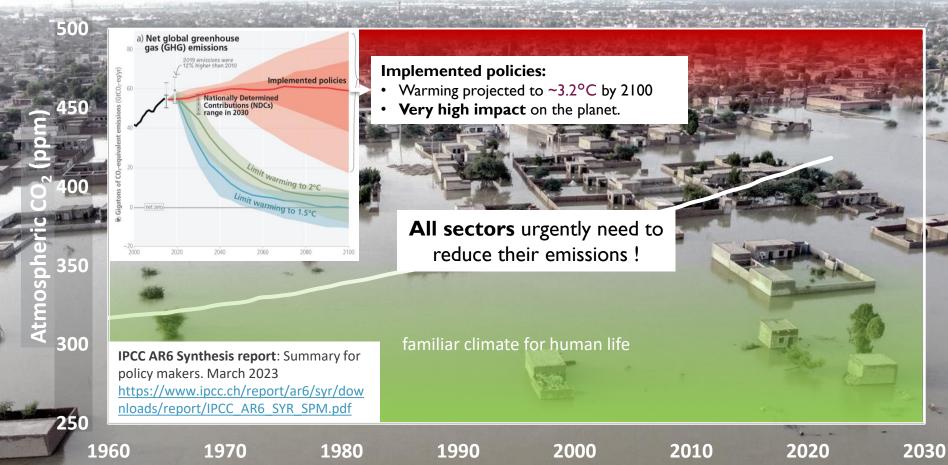

# Need to address emissions, not simply make commitments

Solomon et al., Irreversible climate change due to carbon dioxide emissions, PNAS 2009

Pakistan giant monsoon, Summer 2022 Photo byFida Hussain/AFP

Scripps CO2 Program, 2222

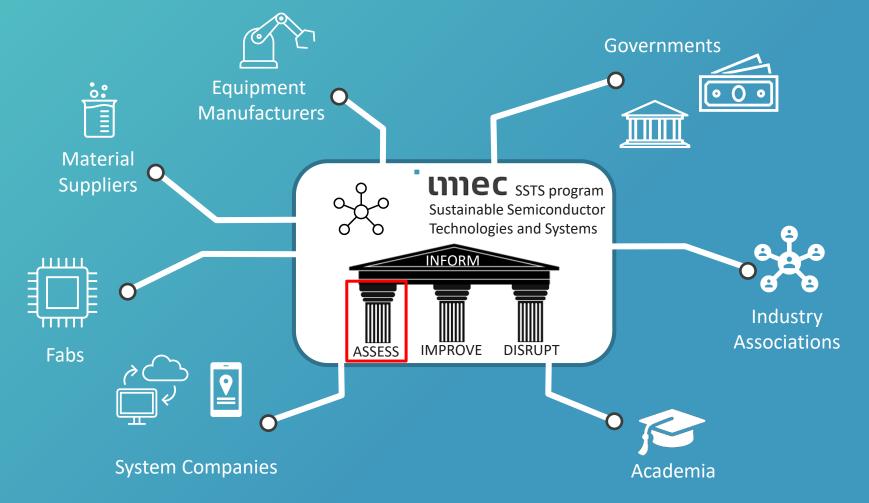

Our mission: Help the semiconductor industry achieve its targets in carbon footprint reduction

## The climate impact of Consumer Electronics manufacturing

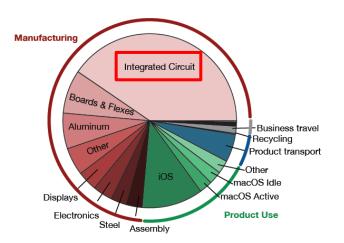

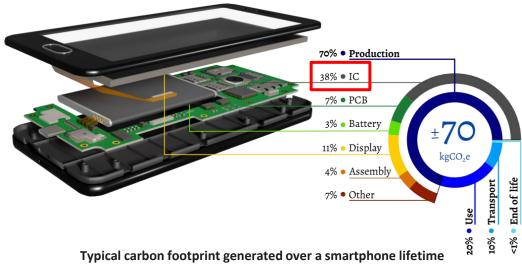

Apple's Carbon-Emission Breakdown Source: Gupta et al., 2021 –The elusive environmental footprint of computing

Source: Moreau et al., 2021 –Could Unsustainable Electronics Support Sustainability?

IC chip manufacturing accounts for the largest share of the climate impact, dominating over product use phase

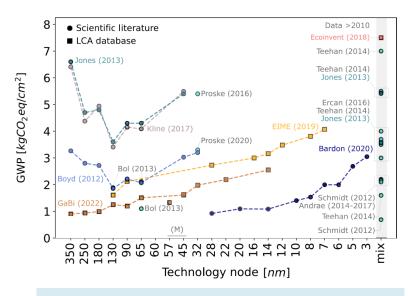

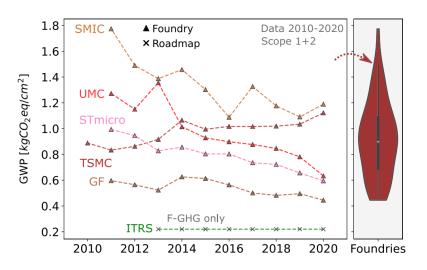

## Scattered data over IC chip manufacturing environmental impact

- Variable Scope

- Variable sources (Primary vs. Secondary)

- Variable approaches (e.g. Bottom-up vs Top-down)

- Data gaps require "creative" plugging methods

#### **Industry data from public CSR reports:**

- Top-down, primary sourced data

- Aggregated over entire company operation, not "per chip" or "per-node"

- Limited scope

- Non-transparent methodology

Source: Pirson et al., 2023 – The Environmental Footprint of IC Production: Review, Analysis, and Lessons From Historical Trends

## Imec ambition for the SSTS Assess pillar

Close the data gap by providing quality, transparent data on environmental impact of IC chip fabrication in a generic high volume manufacturing plant

## imec.netzero

# a Virtual Fab model for environmental impact assessment

#### **Expand the analysis** to:

- Identify high impact problems to focus Improve efforts

- Project the future impact of IC chip manufacturing

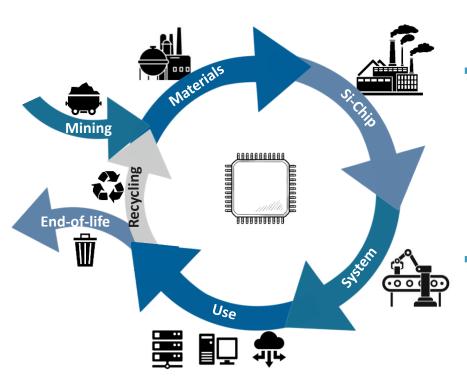

## The Life-Cycle of a Si-chip

Goal and scope of imec.netzero

- Product system Si chips from HVM

- Serving several applications (Logic, memory, etc.)

- Multiple (future) technology nodes

#### Functional Unit

- For Manufacturing industry: "per Wafer"

- For IC Chip users:

- "per functional die"

- "per functional cm²"

- "per transistor"

#### Impact categories

- Current focus:

- Climate Change

- Under development:

- Abiotic resource depletion

- Water scarcity

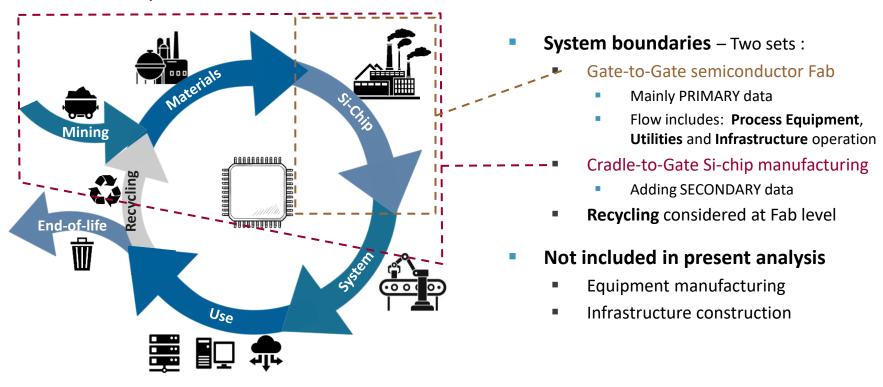

## The Life-Cycle of a Si-chip

Goal and scope of imec.netzero

10

## The Life-Cycle of a Si-chip

Goal and scope of imec.netzero

Data Sources:

**System boundaries** – Two sets :

- Internal imec

- SSTS partners

- LCA databases

- Industry associations: SEMI, ...

- Public organizations: IPCC, IEA, ...

11

- Scientific literature

- Questionnaire to supply chain

semiconductor Fab

IMARY data

ides: Process Equipment, nd Infrastructure operation

Si-chip manufacturing

CONDARY data

sidered at Fab level

resent analysis

anufacturing

construction

public

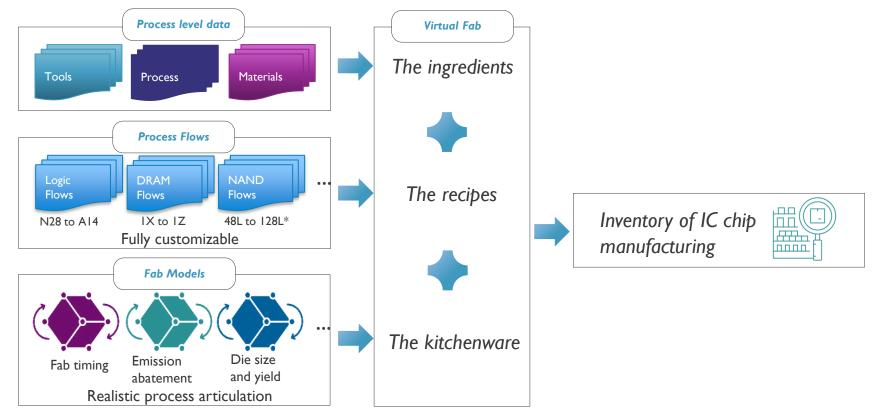

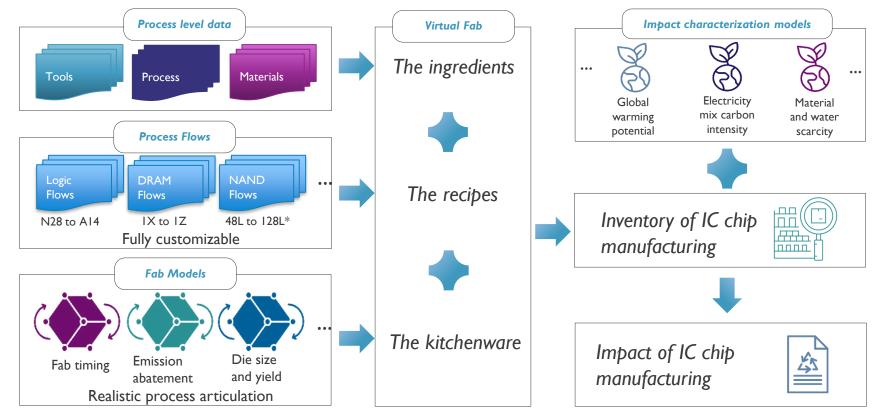

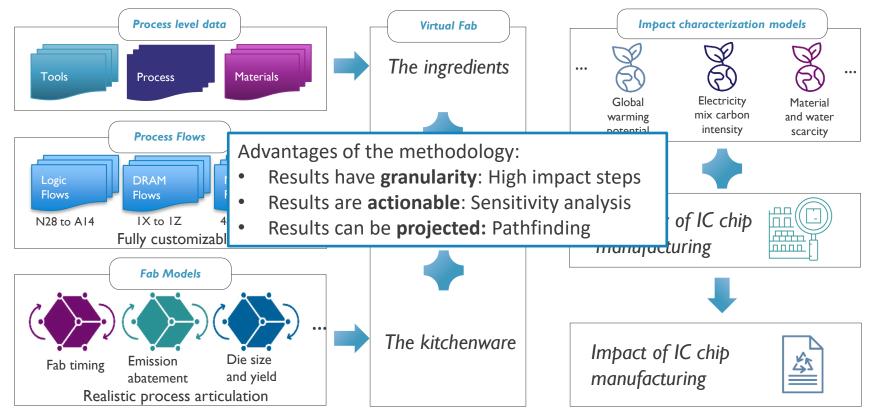

## **SSTS Assess** - Virtual Fab Model

### Quantify the footprint of a chip

### **SSTS Assess** - Virtual Fab Model

### Quantify the footprint of a chip

### **SSTS Assess** - Virtual Fab Model

## Quantify the footprint of a chip

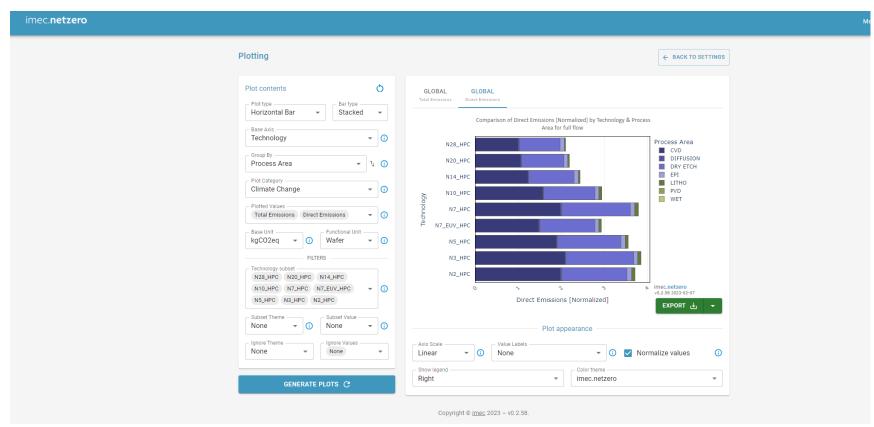

## imec.netzero Web Application

Public version release: June 30

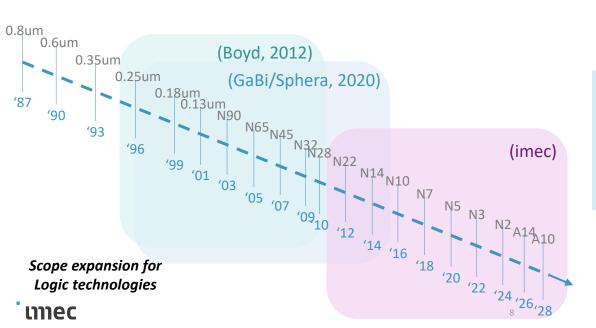

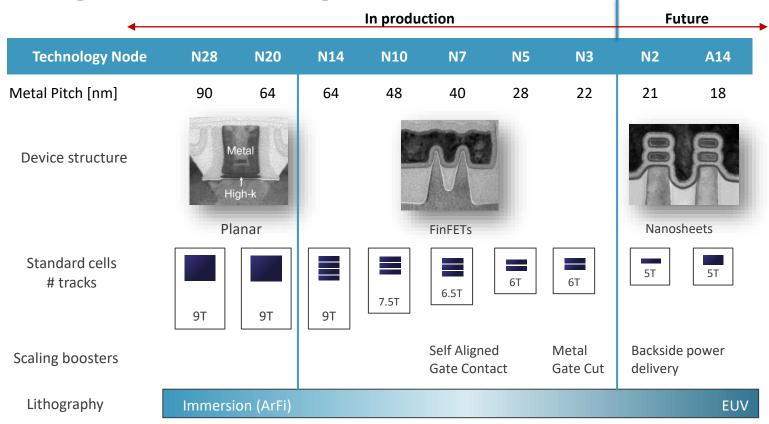

## Studied Logic CMOS technologies and nodes

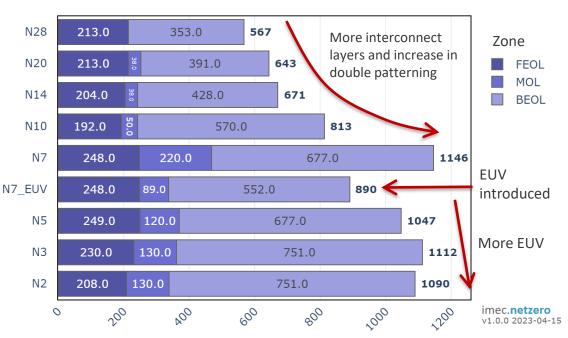

## Complexity Increase of a Mobile SoC

Number of process step evolution per node

- Increase in Complexity node to node where BEOL interconnects dominate

- Introduction of EUV slows down the increase in complexity:

- Less multi-patterning DUV immersion steps

- Less deposition, Dry-Etch, Wet-Clean, Metrology steps

Number of Process Steps

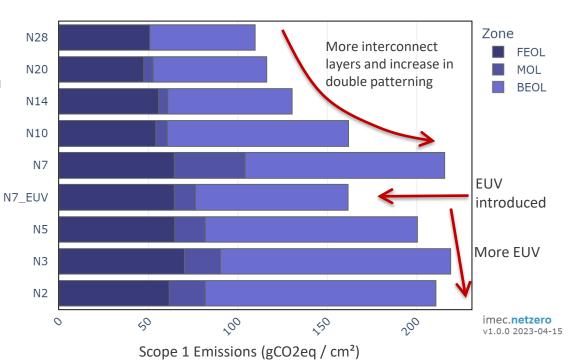

## Direct Emissions (Scope 1)

- Process gases are potent

Greenhouse gases => Deposition

and Etch contribute strongly to

direct emissions

- Multi patterning use many repeats of deposition and etch

⇔ By reducing complexity, EUV keeps direct emissions under check

• 10x10mm<sup>2</sup> die, Murphy yield with 0,15 defect/cm<sup>2</sup>

GHG global warming potential from IPCC AR6

• Tier 2C Abatement model (2019 Refinement to the 2006 IPCC Guidelines for National Greenhouse Gas Inventories)

public

18

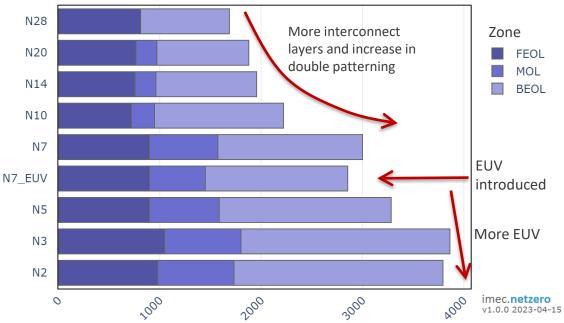

## **Electricity consumption**

- Increase in process complexity directly leads to increased electricity consumption

- Introduction of EUV leads to:

- Reduce in process complexity

- Increased electricity

consumption of the litho

process area

These two effect counteract each other leading to a continued increase.

Electricity consumption (Wh / cm²)

- I 0x I 0mm² die, Murphy yield with 0, I 5 defect/cm²

- Utility electricity consumption modelled using SEMI S23 standard

- Tool Utilization assumed using SEMI S23 standard

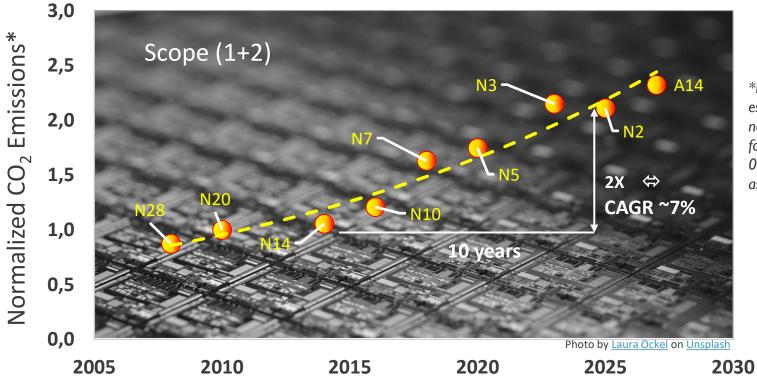

## Carbon Emissions for Semiconductor Manufacturing are Increasing

\*imec.netzero: emissions estimate of imec process nodes representative of foundry nodes.

0.49kgCO<sub>2</sub>eq/kWh assumption for electricity

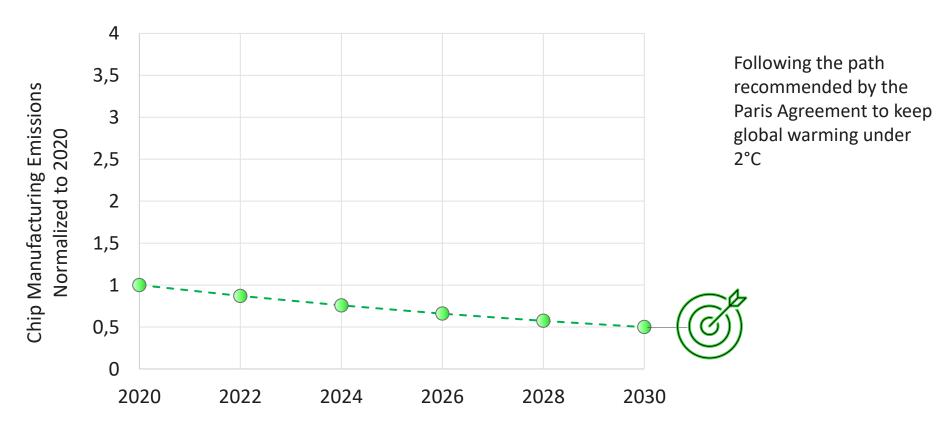

## Ideal climate impact scenario for Semiconductor Manufacturing

21

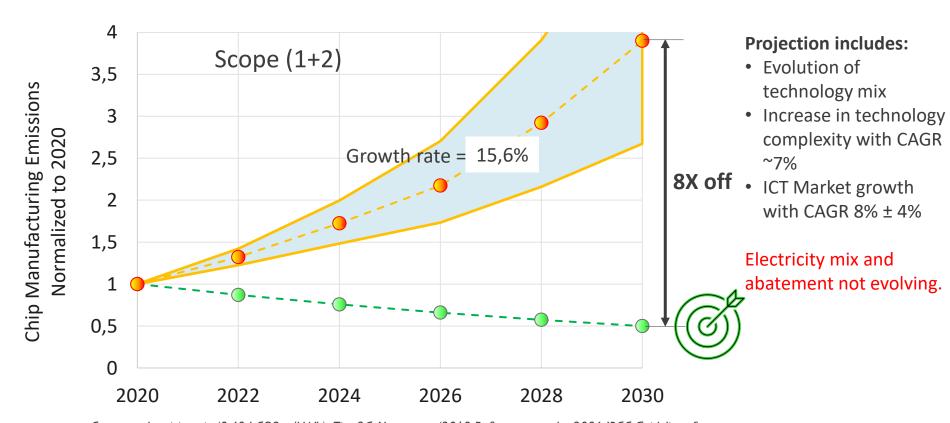

## "Do Nothing" Scenario for Semiconductor Manufacturing

Constant electricity mix (0.49 kCO2eq/kWh), Tier 2C Abatement (2019 Refinement to the 2006 IPCC Guidelines for National Greenhouse Gas Inventories) and GHG global warming potential (IPCC AR6). Volume technology mix from IBS "Foundry Market Trends and Strategic Implications" Vol 30, N 12, Dec 2021. Logic nodes only.

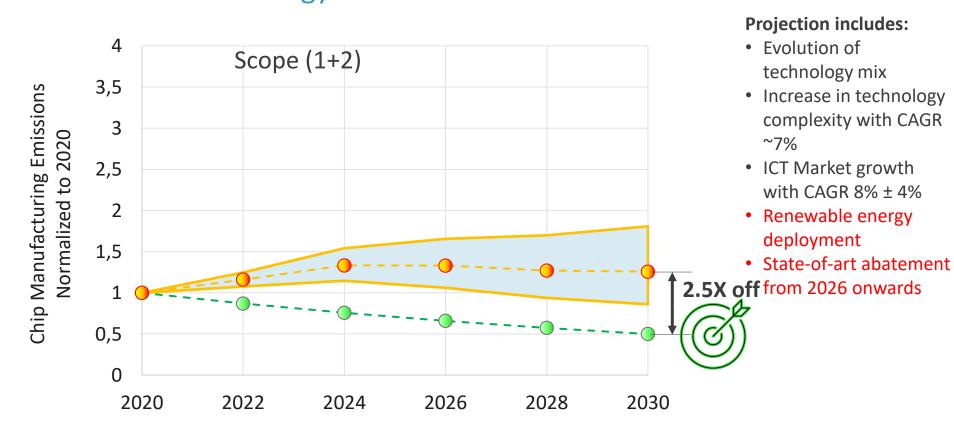

## With Renewable Energy and State-of-the-Art GHG Abatement

Adding to previous slide: Renewable Energy deployment according to IEA and abatement according to IPCC assumed for the years 2020-2024, State-of-the art Abatement from 2026.

## Data enables Action across the industry ecosystem

## Acknowledgments: The SSTS team and supporters

Many great colleagues across imec organization

#### SSTS Team

Alexander Dockx, Andrea Firrincieli, Benjamin Vanhouche, Bertrand Parvais, Bram Vangestel, Emily Gallagher, Farrukh Yasin, Gioele Mirabelli, I-Yun Liu, Konstantina Filippidou, Laurent Van Winckel, Lizzie Boakes, Marie Garcia Bardon, Nora Maene and Lars-Åke Ragnarsson

#### SSTS Supporters

- Alessio Spessot, Arnaud Furnémont, Frank Holsteyns, Hans Lebon,

James Myers, Luca Di Piazza, Sri Samavedam, Tru Lefevere

- The BD, Legal, ICT, APPM, CMT, FABENG, FAIN and LTE teams

#### SSTS Partners

# mec

embracing a better life