**Building flexible SoCs**

Shanghai, China September 14<sup>th</sup> 2017

Julien EYDOUX

Technical Interface Director

## Company

- HeadQuarter: France

- 10 years company

- Only focus on eFPGA

- Patented technology

- Silicon on different foundries and nodes

- Customers

- China commercial: Jiatao

- Staff of 15 people

- Currently hiring (6 open positions)

- Capital: 7M\$

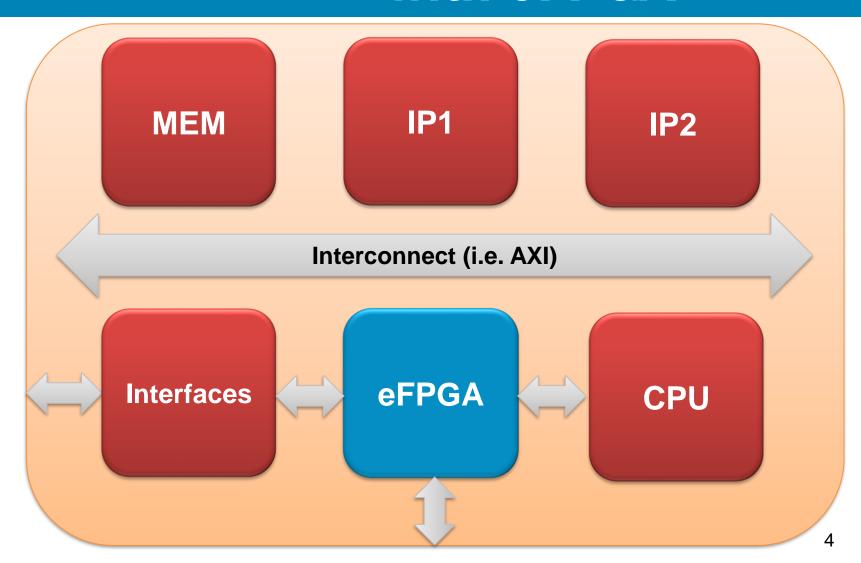

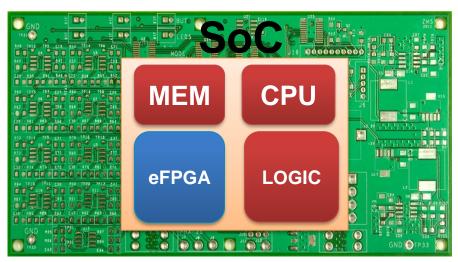

## System On Chip with eFPGA

## eFPGA application scenarios

Co-processor:

- Al

- Automotive

- Data center

MCU variants

Sensor Hub

Security / Cryptography

Signal Processing

## SOC + FPGA vs SOC with eFPGA

- Latency

- Power

- Cost

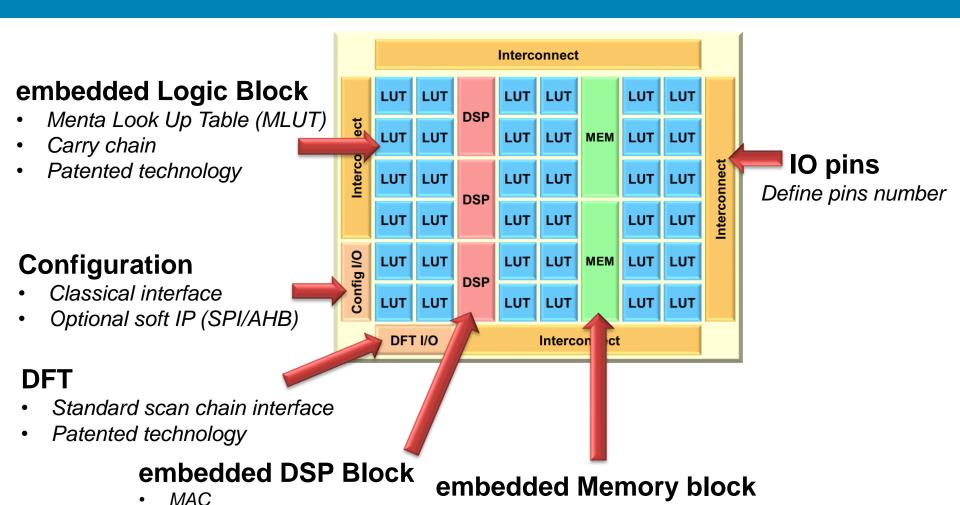

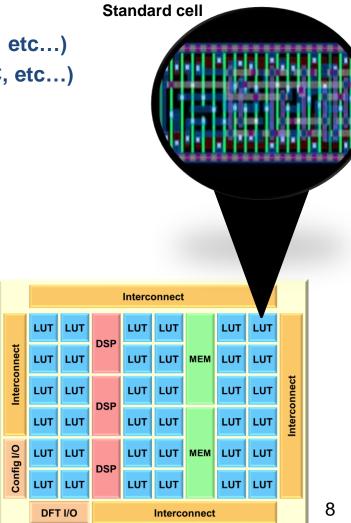

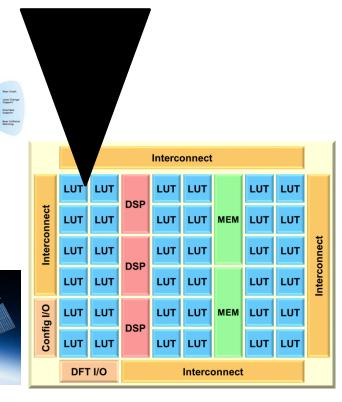

## Menta 4th Generation eFPGA

- Complex DSPCustomer/3rd Party DSP

- From Memory compiler (Foundry/Mem/Customer Provider)

- Type and size can be choosen

## 100% Standard Cell Trusted eFPGA Hard-Macro

- 100% standard cell based

- From Std Cell provider library (Synopsys, ARM, etc...)

- Or from Foundry library (TSMC, GF, SMIC, UMC, etc...)

- Or from Customer library

- Standard EDA integration:

- No Blackbox

- Full Gate Level netlist Simulation

- STA + timings accuracy

- Power accuracy

- ATPG + vector files

- Cadence/Synopsys/Mentor compatibility

**Customer can verify every stage**

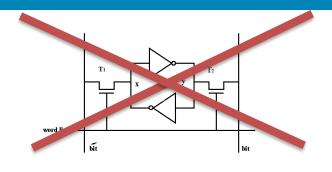

## Trusted configuration Not SRAM based

#### SRAM eFPGA # SRAM Compiler

#### SRAM eFPGA

- SRAM dedicated cell must be developed

- DFT not standard => custom DFT

- Characterization and testchip

#### MENTA

- Use Standard-Cell Register technology

- Patented architecture

- Standard DFT (managed by EDA tools): FC=99.9%

- Very fast test time => low cost test

- Standard verification

- High Yield

- Less prone to radiation errors (SEU)

- Don't need characterization or testchip

# Trusted Standard Integration

### flexible eFPGA

- Foundry & node

- Standard cells provider

- Voltages

- VT flavors

- Metal stack

Power and Speed Trade-off

**Up to 500k equivalent ASIC Gates**

eFPGA fabric

- Form factor

- # IOs

- # LUTs

- DSP:

- Menta 18bits MAC

- Menta Complex DSP

- Customer blocks

- Memory # & types

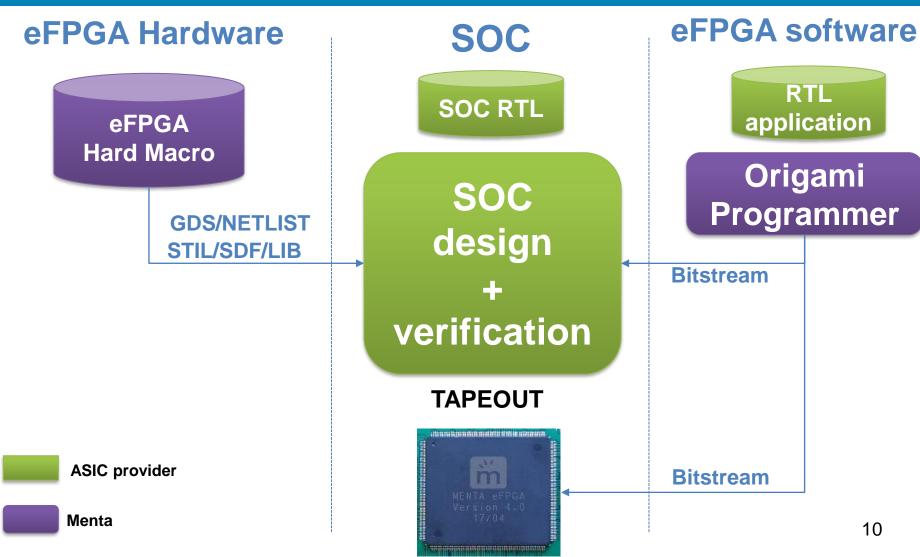

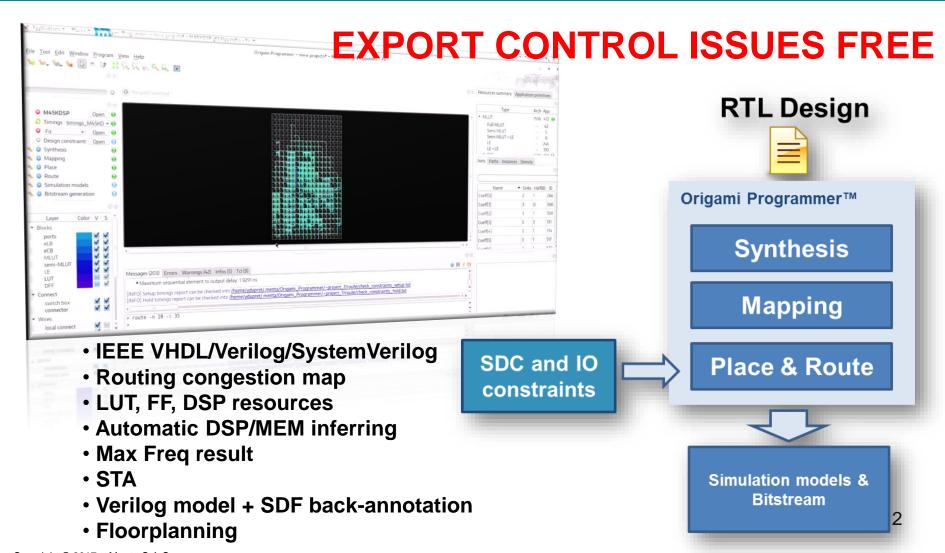

# Trusted Programming Software

### **Menta offers**

#### **Pre-defined IP Menta (IPM)**

Off-the-shelf eFPGA IP

Family of 5 optimized IPs

- From 7K to 60K equivalent ASIC gates

- Physical IP (GDSII)

**Packaged with Origami Programmer**

## **Menta offers**

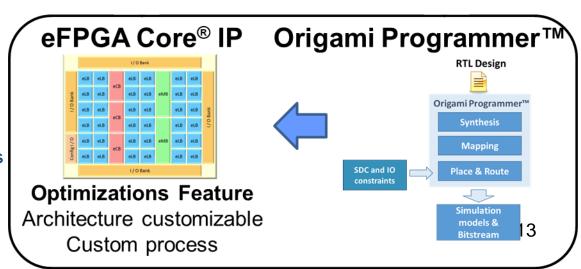

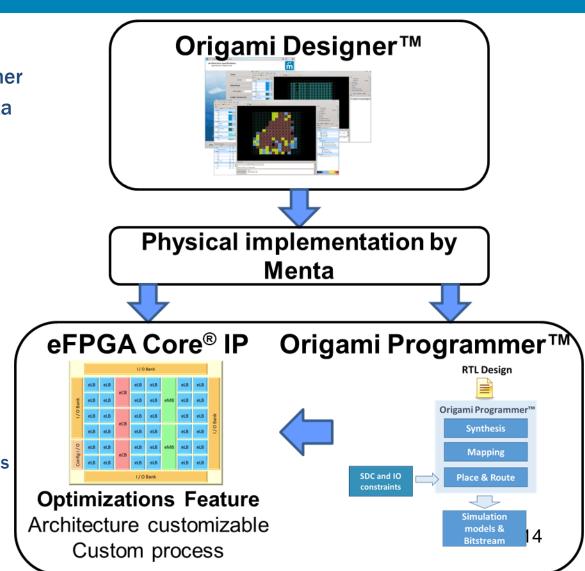

#### **Dedicated eFPGA IP**

eFPGA designed with Origami Designer and physically implemented by Menta Menta deliverables:

- Up to 500K equivalent ASIC gates

- eFPGA dedicated array

- Physical Hard-Macro (GDSII)

Packaged with Origami Programmer

## Pre-defined IP Menta (IPM) Off-the-shelf eFPGA IP

on-the-shell errga ir

Family of 5 optimized IPs

- From 7K to 60K equivalent ASIC gates

- Physical IP (GDSII)

Packaged with Origami Programmer

julien.eydoux@menta-efpga.com www.menta-efpga.com

Our partner in China See us at our Booth