AI驱动的设计应用

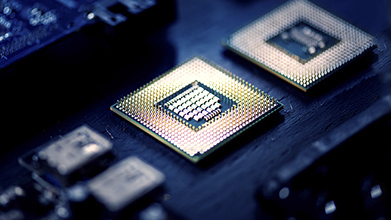

Chiplet是摩尔定律放缓情况下,持续提高SoC高集成度和算力的重要途径。目前业内已有多家企业发布了基于Chiplet技术的芯片,Chiplet俨然已成为各芯片厂商进入下一个关键创新阶段并打破功率-性能-面积(PPA)天花板的一个绝佳技术选择。

采用Chiplet的方式,可将不同功能的芯片通过2D或2.5D/3D的封装方式组装在一起,并可以以异构的方式在不同工艺节点上制造,但是到目前为止,实现Chiplet架构一直非常困难。为了做到这一点,采用这一技术的早期厂商已将单片式芯片设计方法应用于内部定义的设计与验证流程,并开发了自己的接口技术。但是,非聚合裸片市场(即具备类似即插即用的灵活性及互操作性)的发展离不开行业标准和生态系统。通用Chiplet互连技术(UCIe)规范可以实现Chiplet的可定制与封装级集成,可以说是Chiplet发展前路的一大助推剂,UCIe正在帮助我们迅速紧跟这种面向先进应用的全新设计方式。

Chiplet技术为何腾飞?

随着对芯片性能的要求日益提高,需要在更小的空间里集成更多的晶体管,SoC的尺寸正在接近芯片制造的上限。传统的单片SoC变得太大且成本过高,无法通过先进设计进行生产,并且良率风险也随之攀升。而Chiplet技术将SoC组件分开制造,再封装到一起,则可以降低成本,减少浪费,并大大改善可靠性。

除了在不同工艺节点支持最适合特定功能的不同组件外,Chiplet架构还允许将数字、模拟或高频工艺的不同裸片集成到一起,还可以在设计中加入高度密集的3D内存阵列,即高带宽内存(HBM)。

假设您需要开发一部设备,该设备的I/O接口(如以太网接口等)可能并不需要最前沿的工艺。按照Chiplet技术的思路,您可以在一个细化的层面以“形式遵循功能”的思路优化PPA,如果在不同的设备上使用的I/O子系统是一样的,还可以一次性制造所有I/O接口,从而借助生产规模获得更低成本。相比之下,如果整个SoC都位于同一裸片上,无论功能如何,I/O接口都要与您最先进的功能采用相同的工艺,除了制作成本增加外,一旦设计中的某个组件出现故障,就会导致整体失效。

规模和模块化所带来的灵活性,也将帮助您应对不断缩小的上市时间窗口。具有标准功能的裸片可以混合并匹配,即获得一种硬IP,从而让您的工程人才专注于设计的差异化因素,以加快产品上市速度。

虽然上面的方式听起来十分理想,但各个独立的裸片在带宽、互操作性和数据完整性方面具有很大差异,目前只有那些拥有足够资源来支持裸片间定制互连开发的大公司才会采用这种技术。但是随着这种更前沿设计方法的普及,裸片间的互连在本质上已经与互操作性相抵触。

尽管存在这些挑战,预计到2024年,Chiplet市场的规模将增长至500亿美元;而UCIe则是这一增长的关键推动力。

UCle为何成为Chiplet设计的首选标准?

其实为了应对Chiplet设计中所面临的挑战,行业出现了几种不同的标准。但是UCIe是唯一具有完整裸片间接口堆栈的标准,其他标准都没有为协议栈提供完整裸片间接口的全面规范,大多仅关注在特定层。而且UCIe支持2D、2.5D和桥接封装,预计未来还会支持3D封装。

UCIe不仅能满足大部分每引脚8Gbps至16Gbps的设计,还能满足从网络到超大规模数据中心等高带宽应用中每引脚32Gbps的设计;换言之,该标准将满足当前和未来的带宽发展。UCIe有两种不同的封装类型:

- 用于先进封装的UCIe,如硅衬垫、硅桥或再分配层(RDL)扇出

- 用于标准封装的UCIe,如有机衬底或层压板

UCIe堆栈本身拥有三层:

- 最上端的协议层通过基于流量控制单元(FLIT)的协议实现,确保最大效率和降低延迟,支持最流行的协议,包括PCI Express®(PCIe®)、Compute Express Link(CXL)和/或用户定义的流协议。

- 第二层用于对协议进行仲裁与协商,以及通过裸片间适配器进行连接管理。基于循环冗余检查(CRC)和重试机制,该层还包括可选的错误纠正功能。

- 第三层为物理层(PHY),规定了与封装介质的电气接口,是电气模拟前端(AFE)、发射器和接收器以及边带通道允许两个裸片之间进行参数交换与协商的层级。逻辑PHY实现了连接初始化、训练和校准算法,以及测试和修复功能。

EDA厂商推动UCle的发展

作为EDA和IP解决方案的领导者,新思科技已成为UCIe的成员之一,我们期待着未来对UCIe规范做出贡献,与广大UCIe的支持者们积极推动构建健康的UCIe生态系统。为了简化UCIe设计路径,新思科技推出了完整的UCIe设计解决方案,包括PHY、控制器和验证IP(VIP):

- PHY──支持标准和高级封装选项,可采用先进的FinFET工艺,获得高带宽、低功耗和低延迟的裸片间连接。

- 控制器IP──支持PCIe、CXL和其它广泛应用的协议,用于延迟优化的片上网络(NoC)间连接及流协议;例如与CXS接口和AXI接口的桥接。

- VIP──支持全栈各层的待测设计(DUT);包括带有/不带有PCIe/CXL协议栈的测试平台接口、用于边带服务请求的应用编程接口(API),以及用于流量生成的API。协议检查和功能覆盖位于每个堆栈层和信令接口,实现了可扩展的架构和新思科技定义的互操作性测试套件。

新思科技的解决方案不仅带来了稳健、可靠的裸片间连接,并具有可测试性功能,可用于已知良好的裸片,和用于纠错的CRC或奇偶校验。它将使芯片设计企业能够在Die间建立无缝互连,实现最低的延迟和最高的能效。

对于Chiplet设计,由于多个流协议而增加的有效载荷可能需要数天甚至数月的时间来实现仿真,从而限制了其实用性。对此,新思科技还推出了UCIe的验证IP,用户需要首先创建各种单节点和多节点模型,模拟这些简化的系统以检查数据的完整性。利用新思科技 ZeBu®仿真系统在具有多协议层的更高级别系统场景中进行测试,然后再使用新思科技 HAPS®原型验证系统进行原型设计。新思科技的验证IP从模型到仿真、模拟,再到原型验证确保芯片投产前的无缝互操作性。

在摩尔定律逼近极限的今天,Chiplet的发展已是大势所趋,不过其前路仍然面临着不少挑战,需要产业界各个产业链的厂商支持,才能最终迎来其发展腾飞。