Industry Expert Blogs

|

Enhance safety with TessentLee Harrison - Siemens - Tessent Embedded AnalyticsFeb 01, 2024 |

Why ICs designed with Tessent enhance automotive functional safety.

Quality, safety, security and reliability and are key considerations when designing ICs. For advanced ICs targeted to the automotive, aerospace or medical sectors, the process of designing, manufacturing, testing, and in-life monitoring is extremely complex. The challenges range from adherence to standards and regulations, managing capital investments and engineering resources, securing the right tools and flows, and establishing methods to manage the vast amounts of data that inform each step in the lifecycle of the device. Tessent solutions help you ensure high SoC quality, enhance safety, optimize security and increase reliability so you can get your product to market faster.

Today, let's talk about why ICs designed with Tessent enhance automotive functional safety.

Why focus on safety

Automotive ICs are increasingly developed and manufactured using cutting-edge processes. These devices are no longer only deployed for simple functions like controlling windows or light signaling but are now required for complex functions related to advanced driver-assist systems (ADAS) and increasingly for autonomous driving applications. These advanced functions require a lot of processing power, which demands very large and complex ICs manufactured for optimal power efficiency. This, coupled with the need for these devices to meet the stringent safety requirements of the ISO 26262 standard, is resulting in a new set of challenges for automotive device and systems manufacturers. Solutions are needed to ensure new complex automotive electronic systems operate safely at all times throughout the life of the vehicle and when they do fail, they fail safely. This is known as functional safety.

Functional safety is defined by the ISO 26262 standard as the "absence of unreasonable risk due to hazards caused by malfunctioning behavior of electrical/electronic systems." Safety used to be addressed by the automotive tier 1s and OEMs, but increase complexity means that functional safety is now a concern of the semiconductor and IP companies too.

IC designers can enhance functional safety by using the tools that will ensure success and reduce risks by automating compliance to relevant standards and regulations and performing in-life fault detection.

Logic BIST

Logic built-in-self-test (BIST) is used to ensure that semiconductor devices are defect-free after manufacturing. However, logic BIST usually can't reach the same test quality and coverage as ATPG without the addition of test points in the design to help the detection of random resistive faults. Ensuring zero-defect chips at manufacturing relies on advanced fault models for scan test.

For functional safety, you need to ensure that the device is defect free for its entire operating life. Logic BIST has the advantage of being able to generate test patterns internally, making it a good solution for an in-system test solution that can be used as a functional safety mechanism. Logic BIST has a very high diagnostic coverage (DC) for the logic under test and is proven to be an extremely effective safety mechanism. Additionally, the Tessent logic BIST IP is ASIL-D ready certified, so designers can have more confidence in the solution.

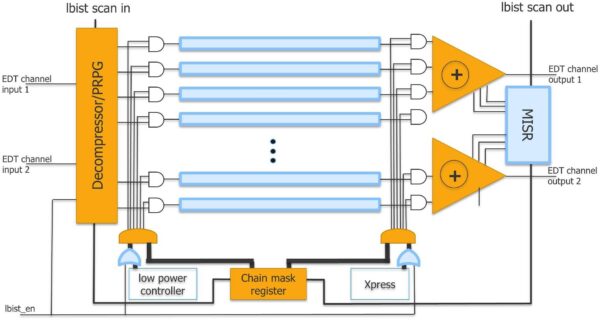

Tessent Logic BIST can be used as part of a hybrid approach with scan ATPG compression where the two different test systems share much of the same logic structures (figure 1).

One issue with logic BIST during in-life testing is that for a large enough design size and pattern set, it could be impossible to meet the diagnostic time interval (DTI) requirements specified by ISO 26262. Tessent Logic BIST uses Observation Scan Technology (OST) to drastically reduce the logic BIST test time for automotive ICs. Logic BIST with OST uses test points in the design to accumulate test coverage on every clock cycle (both shift and capture), rather than just accumulating coverage on a per-pattern basis. Customers have seen up to 20X reduction in test pattern count needed to achieve target test coverage. This reduction in pattern count reduces the time it takes to detect faults, which opens the possibility of achieving higher ASIL certification. You can learn more about how Infineon used logic BIST with Observation Scan Technology in this video.

Memory BIST

For memories in an automotive SoC, memory BIST is the solution for testing and self-repair of the device during key-on, key-off, and during operation. Traditional memory BIST is destructive: the contents of the memory are destroyed.

Tessent Memory BIST can support a non-destructive memory BIST controller, so the memory under test is not taken offline, its contents do not need to be restored after testing, and there is little to no impact on system performance.

Another important memory BIST capability for automotive is fast built-in self-repair (BISR) register loading. When testing repairable memories, you have to load all the repair registers in the memory BIST configuration. If the device is large, this can add quite a bit of time to the start-up/key-on testing. Automotive OEMs have put limits on how much time you can spend testing at key-on. Tessent Memory BIST loads the BISR registers in parallel to speed up the key-on testing.

Analog fault simulation

A typical automotive IC has some analog IP, which also must have the right levels of coverage to meet ISO 26262 requirements. For ensuring analog fault coverage, Tessent offers an analog fault simulator called Tessent DefectSim. It generates FMEDA (failure modes, effects and diagnostic analysis) metric estimates for use in your ISO 26262 certification process.

Embedded Analytics

We've talked about detecting physical defects in an automotive IC. The Tessent Embedded Analytics monitors functional operation at the system-level. The embedded monitors can gather data on functional buses, memory interfaces, and performance of the device. This lets designers monitor device behavior during the vehicle operation, including the hardware/software interactions. Tessent Embedded Analytics also acts as designed-in cybersecurity that future-proofs vehicles against malicious attacks. Learn more about designing automotive ICs for cybersecurity.

Safety island

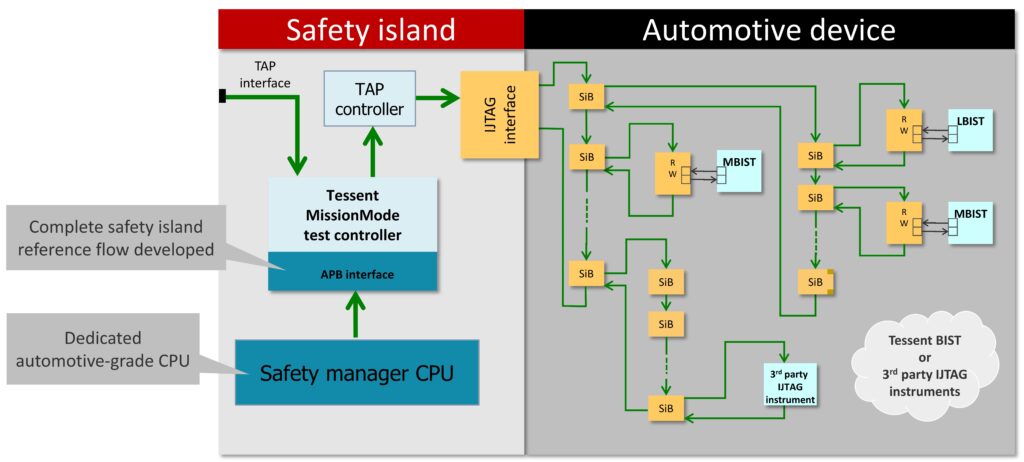

So how to you get the data off the automotive device? Tessent uses a complete Safety Island architecture that comes with a reference flow to ease implementation (figure 2). It's based on a well-defined test controller called Tessent MissionMode, connected to an IJTAG network.

The Safety Island can be expanded to manage more than just the test. You can connect to Embedded Analytics, other functional safety IP and third-party monitors, and let the Safety Island manage and coordinate all the data through a single edge processing device. Once you have the data and can process it in the Safety Island, you could send critical data to the cloud for further analysis. The automotive maker could see data from a whole fleet of vehicles and use that data to inform decisions.

The future of in-system test for automotive safety

Enhancing functional safety at the semiconductor level requires the use of tools that automate the application of safety technologies to the design, test and in-life monitoring of automotive ICs. Tessent offers industry-leading solutions that help designers efficiently meet their safety requirements. All Tessent tools are ISO 26262 are Tcl 1 certified and ASIL-D ready so users can have confidence that the software tools are generating the right output and that the Tessent IP is already certified for use in your design.

In-system test will continue to improve to meet more stringent automotive safety requirements. One opportunity is to use the new Tessent In-system test controller in-system, which would allow delivery of manufacturing quality test to be delivered in-system.