Industry Expert Blogs

|

Rambus CXL IP: A Journey from Spec to Compliance- Rambus, Inc.May 26, 2024 |

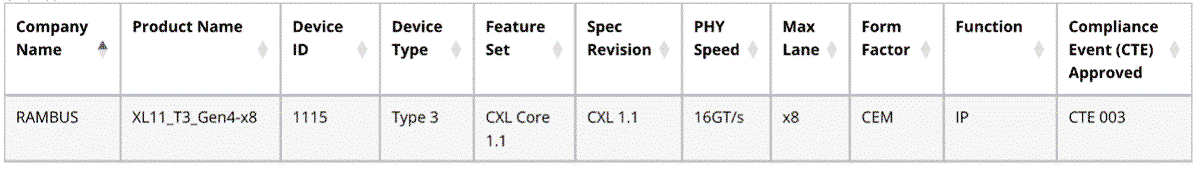

Driven by our unwavering commitment to quality and performance, a Rambus team of engineers, validation experts, and architects have been taking part in CXL� Compliance Test Events to ensure the flawless performance and market readiness of our CXL Controller IP. We are pleased to report that our CXL 2.0 Controller IP has gained compliance in CXL 1.1 and has been added to the Integrators List.

CXL Compliance Program

The CXL Compliance Program provides member companies with opportunities to test the functionality and interoperability of end products as defined in the CXL specification.

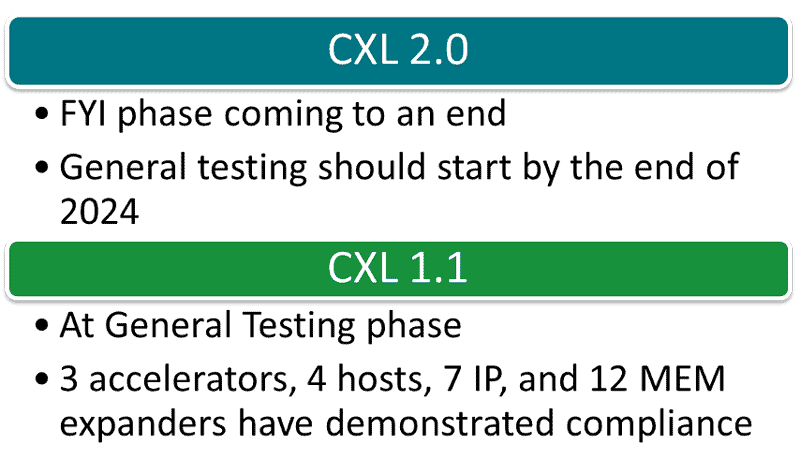

Structured into distinct phases�Pre-FYI (For Your Information), FYI Phase, and General Testing�the CXL Compliance workshops provided us with a comprehensive framework for assessing and validating our CXL Controller IP. We leverage our team's experience to implement the CXL Controller IP in FPGAs as a means to enable interoperability and protocol compliance with other CXL hardware solutions in the ecosystem.

Status of CXL Spec Compliance Phases (as of May 2024)

Four Tests to Compliance

The workshops involved validating four types of tests to claim compliance, ensuring our CXL IP met CXL standards for reliability and performance across various parameters, including interoperability, protocol adherence, and electrical compliance.

1. Interoperability tests involve establishing connections with other equipment present at the event.

- Cross-compatibility: Customers implementing a CXL controller in their ASIC design can leverage our solution's seamless transition from FPGA to ASIC. The identical codebase ensures consistency and facilitates testing and validation in an FPGA environment before ASIC implementation.

- Accelerated Validation: By utilizing our FPGA-compatible IP for prototyping, ASIC clients can expedite validation and bring-up phases.

- Comprehensive Support: We stand by our clients throughout the development journey, offering expertise and guidance from prototyping to final ASIC implementation.